## **B GE Vingmed Ultrasound**

Service Manual - Rev. I – Online –

### System FiVe Sw.: Up to v.1.9.x

Click to choose:

Index

Table of Contents

• Abbreviations, Definitions, Glossary, Terminology, Nomenclature

# The **SYSTEM**FIVE Service Manual

Service Manual.

### **Main Overview**

Introduction

Topics described in this manual

These topics are described in the Service Manual:

This page lists the main topics covered by the  $\ensuremath{\texttt{SYSTEM}}\xspace{FIVE}$

| Subject                                                            | Section  |

|--------------------------------------------------------------------|----------|

| Warnings and Cautions                                              | Intro-5  |

| Table of Contents                                                  | Intro-17 |

| Theory of Operation                                                | А        |

| Block Diagrams – Complete                                          | В        |

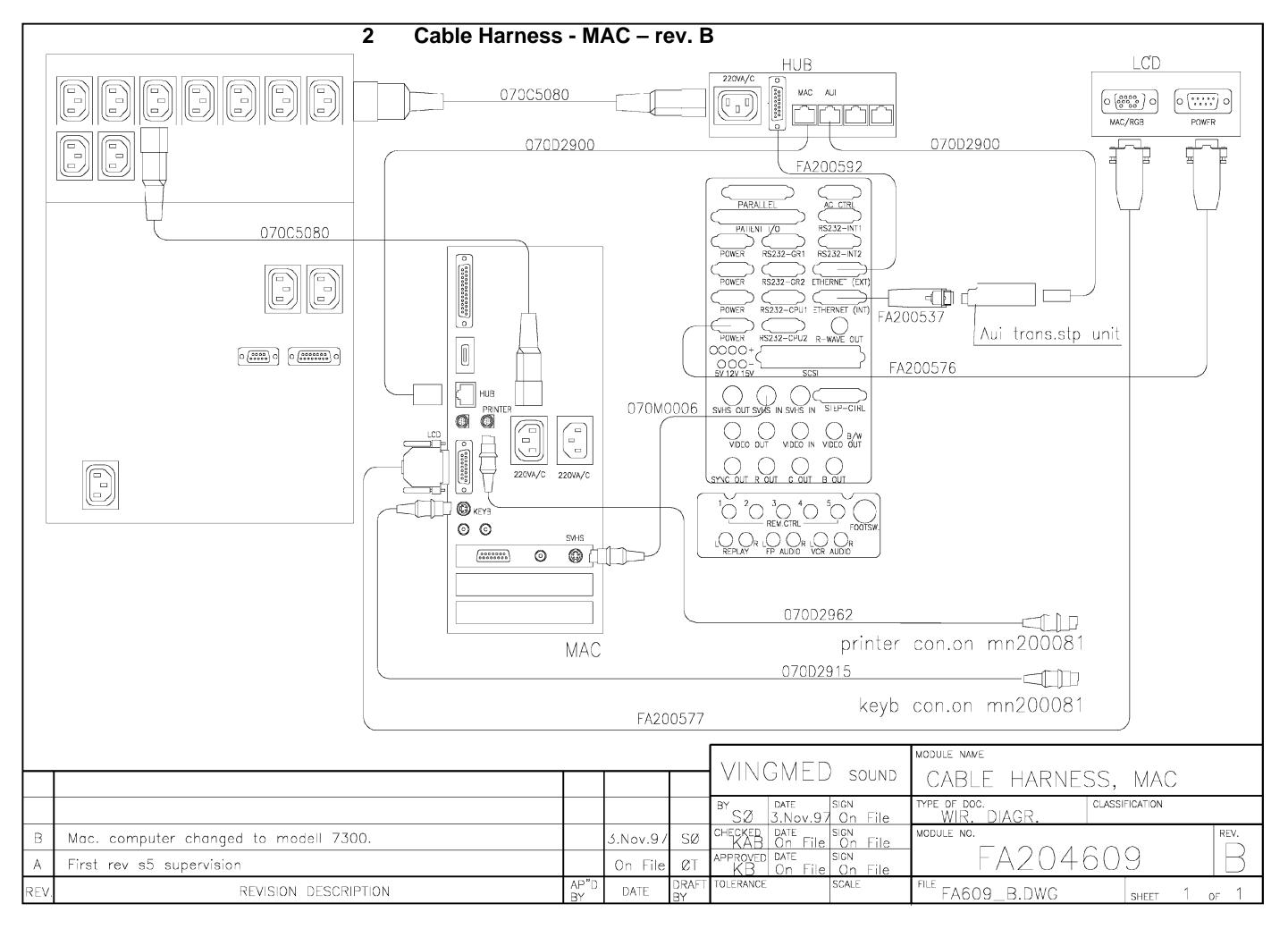

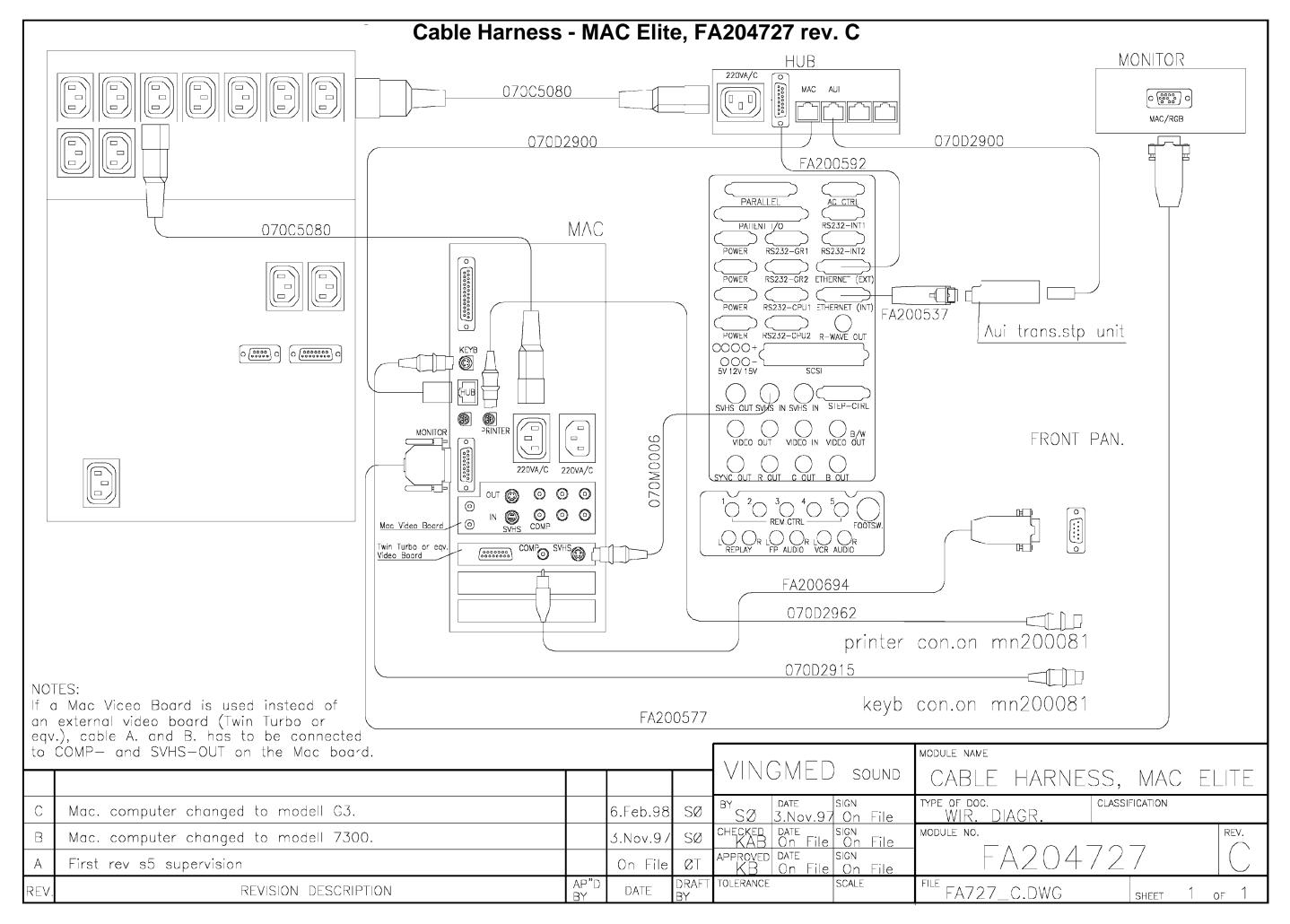

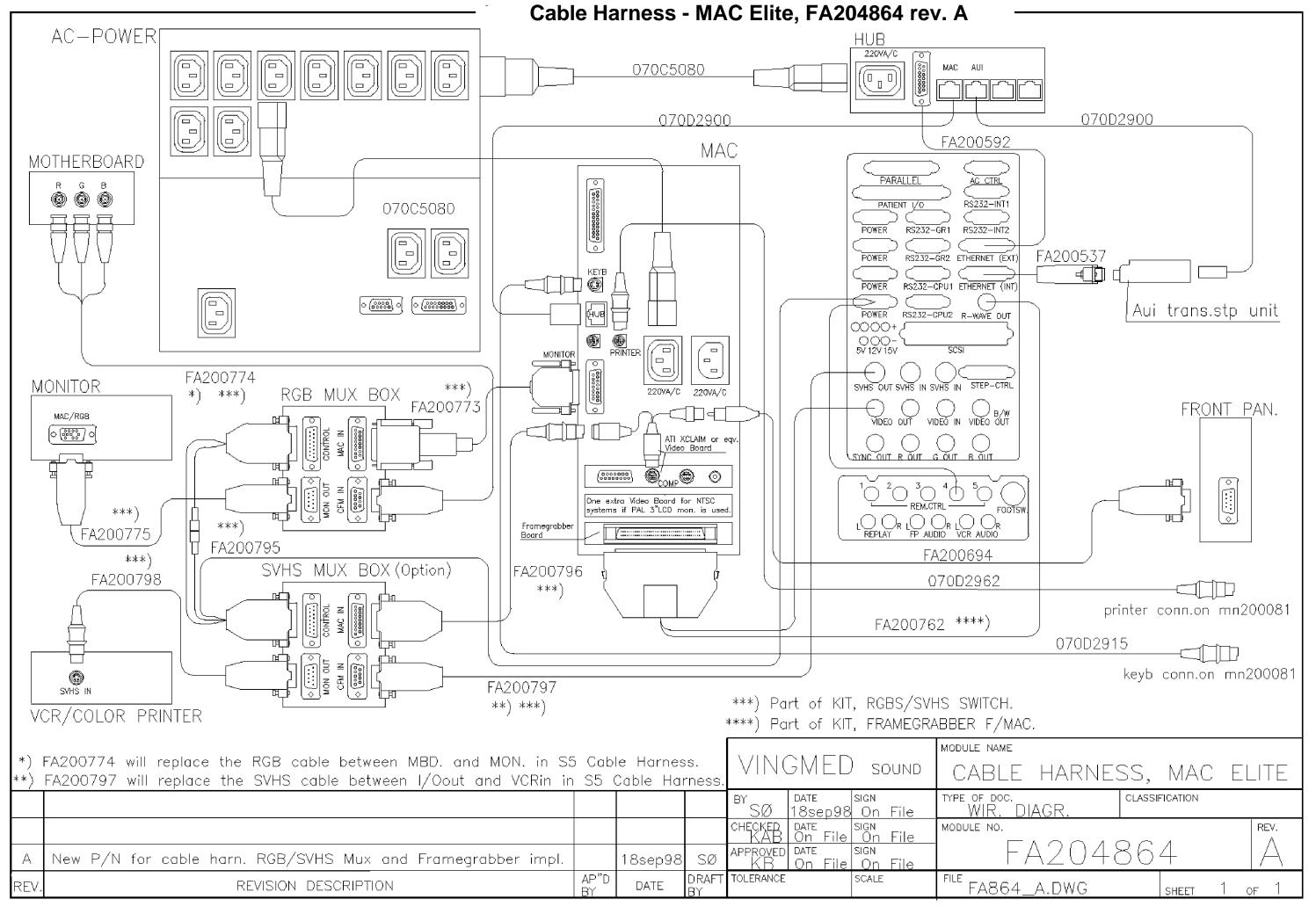

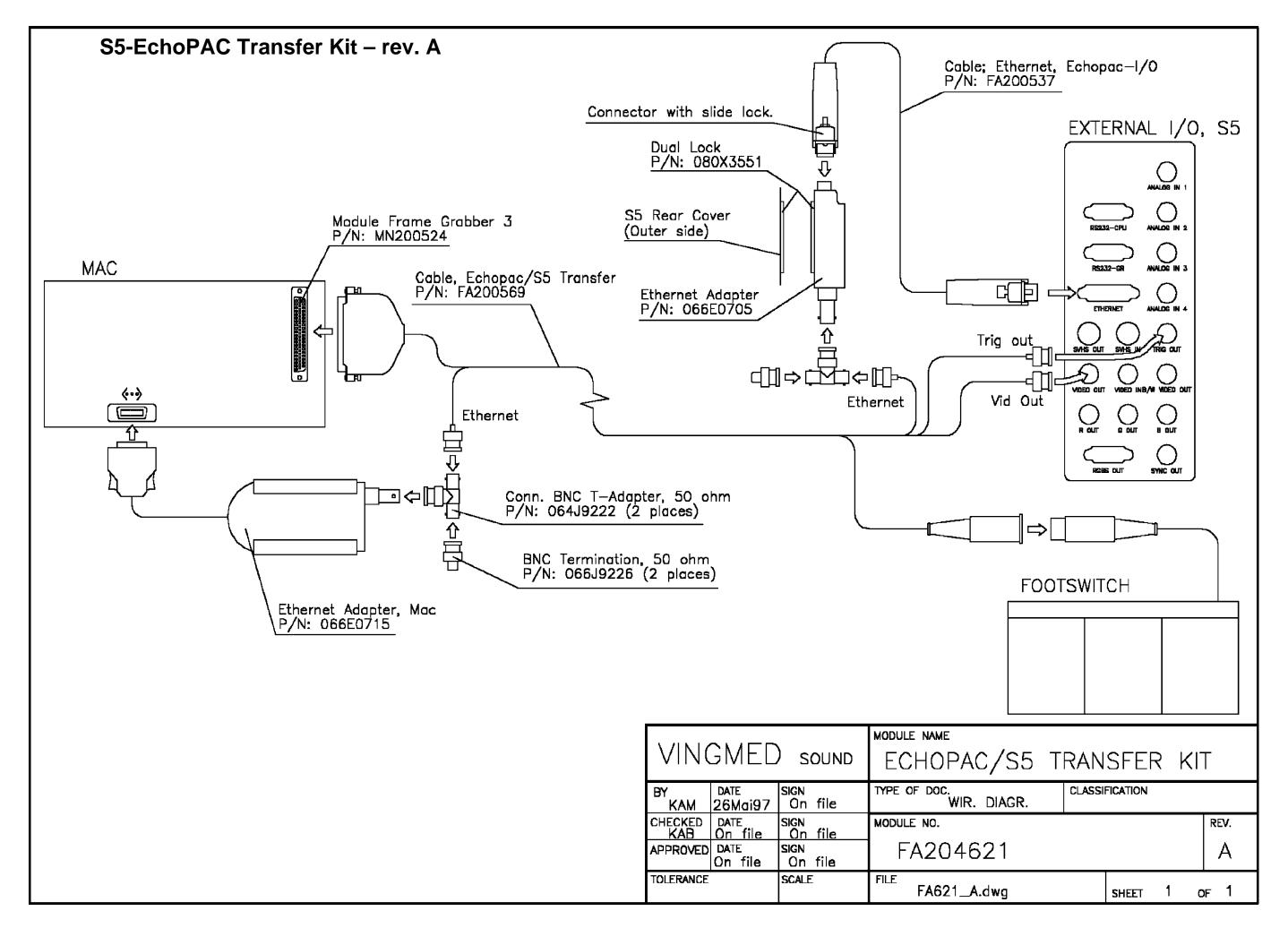

| Cables                                                             | C1       |

| Power                                                              | C2       |

| Mechanics                                                          | D        |

| Probes                                                             | E        |

| I/O signals                                                        | F        |

| Maintenance Procedure                                              | G        |

| Config. & Rev. Control                                             | Н        |

| Revision Req. List                                                 | I        |

| Troubleshooting Guide                                              | K        |

| Replacement Procedures                                             | L        |

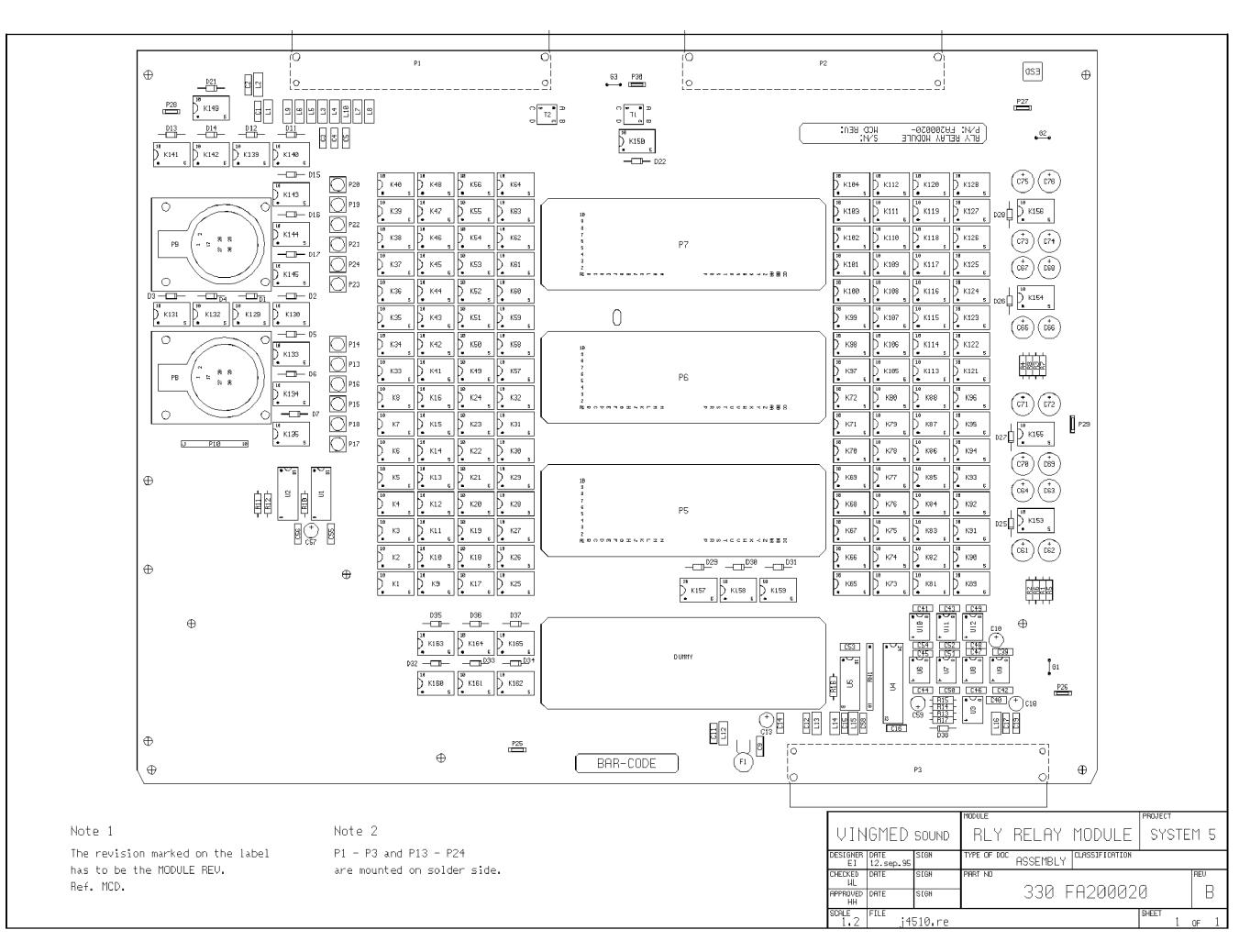

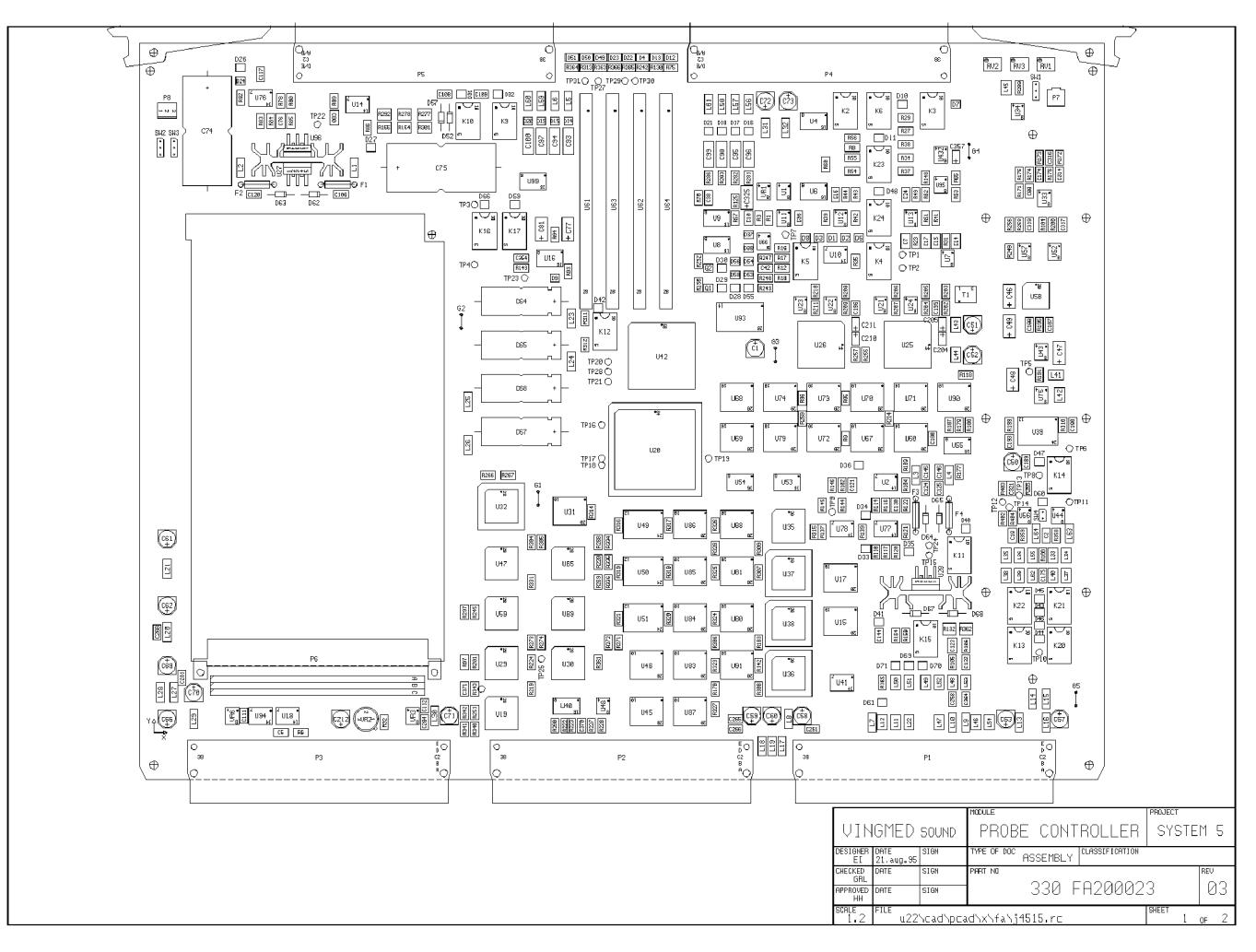

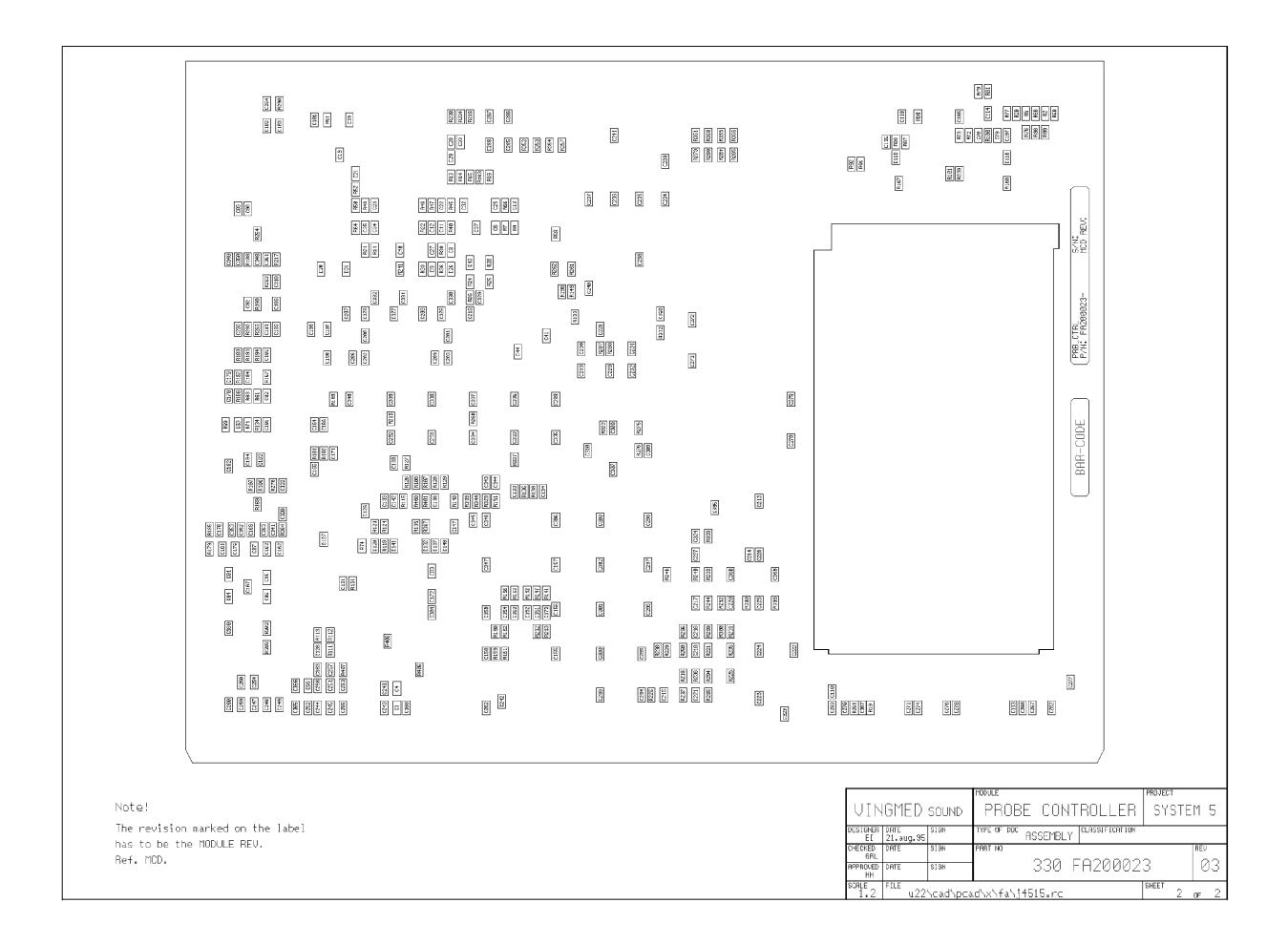

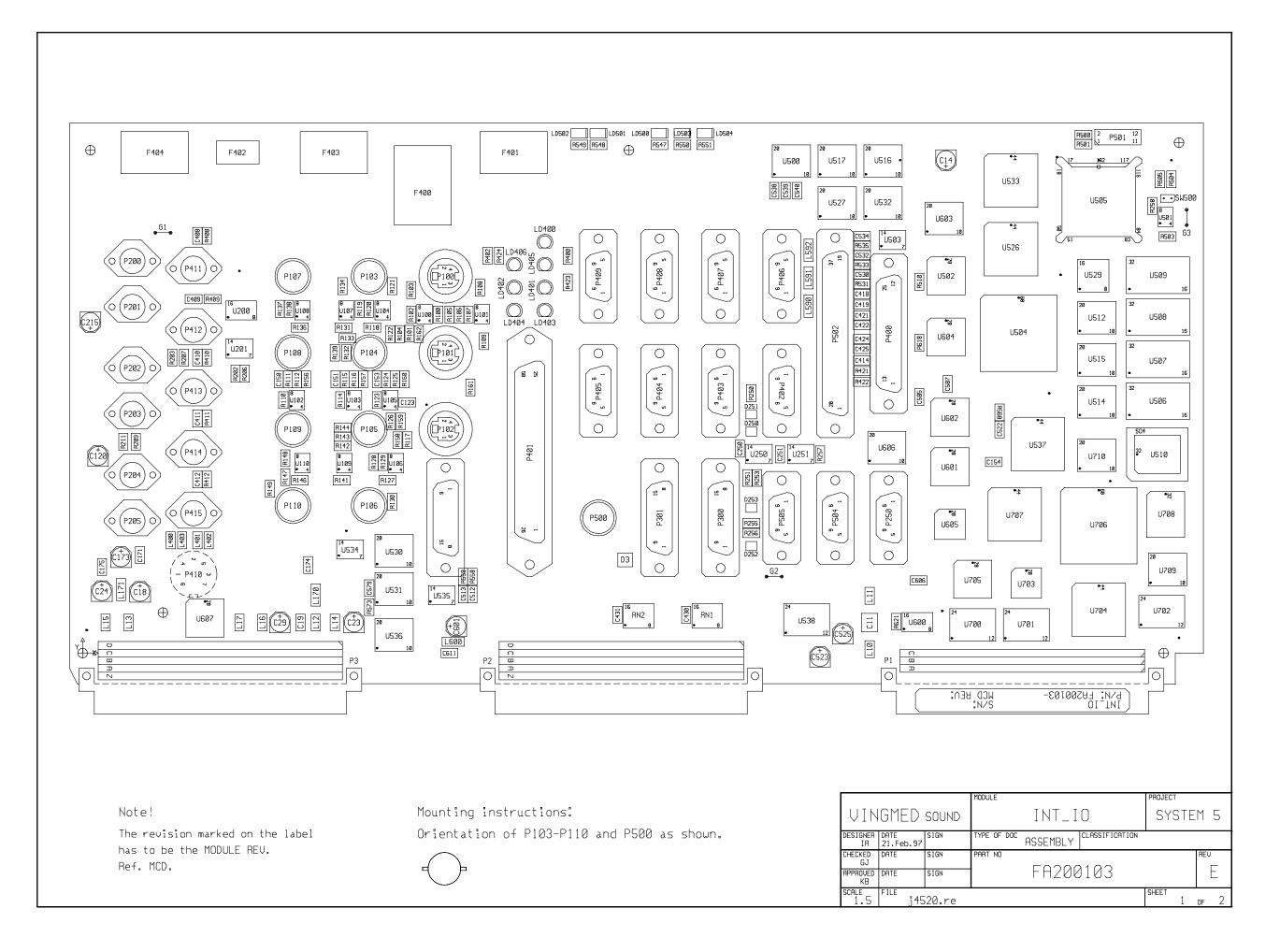

| Board Assembly Drawings - rev 01                                   | М        |

| Software Overview                                                  | Ν        |

| Spare Parts – 02                                                   | 0        |

| Abbreviations, Definitions, Glossary, Terminology,<br>Nomenclature | Р        |

| Index                                                              | R        |

**GE Vingmed Ultrasound**

# **Service Manual**

**Software versions:** Up to v.1.9.x.

Part No.: FA091050 rev. I November 2000

| MANUAL STATUS                                                             | © Copyright 1994 – 2000 by <sup>®</sup> GE Vingmed Ultrasound AIS.                                                                                                                                                                                                          |  |  |  |  |  |  |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Printed in Norway.<br>Eleventh edition.<br>November 2000.                 | All rights reserved. No part of this Manual may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of GE Vingmed Ultrasound A/S. |  |  |  |  |  |  |

| COMPANY DATA:                                                             |                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| GE Vingmed Ultrasound A/S ,<br>P. O. Box 141,<br>N-3191 Horten,<br>Norway | Telephone:         (+47) 3302 1100           Telefax:         (+47) 3302 1350           Telex:         70405 sound n           Internet email:         NORWAYSERV@euromsx.gemse.fr                                                                                          |  |  |  |  |  |  |

# Introduction - rev. 11

### 1 Warnings and Cautions

The following safety precautions must be observed during all phases of operation, service and repair of this equipment. Failure to comply with these precautions or with specific warnings elsewhere in this manual, violates safety standards of design, manufacture and intended use of the equipment.

#### 1.1 Authorization

Operating personnel must not remove the system covers. Servicing should be performed by authorized personnel only. Only personnel who have participated in a System FiVe Training Seminar are authorized to service the equipment.

#### 1.2 Electric Shock Hazard

To minimize shock hazard, the equipment chassis must be connected to an electrical ground. The system is equipped with a three-conductor AC power cable. This must be plugged into an approved electrical outlet with safety ground. If an extension cord is used with the system, make sure that the total current rating of the system does not exceed the extension cord rating.

The power outlet used for this equipment should not be shared with other types of equipment.

Both the system power cable and the power connector meet international electrical standards.

#### 1.3 Dangerous Procedure Warnings

Warnings, such as the example below, precede potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed.

#### WARNING

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing and adjusting.

#### 1.4 Explosion Warning

Do not operate the equipment in an explosive atmosphere. Operation of any electrical equipment in such an environment constitutes a definite safety hazard.

#### 1.5 Electrostatic Discharge Warning

Do not touch any boards with integrated circuits prior to taking the necessary ESD precautions:

- 1. Always connect yourself, via an arm-wrist strap, to the advised ESD connection point located on the card rack.

- 2. Follow general guidelines for handling of electrostatic sensitive equipment.

#### 1.6 Do not substitute parts or modify equipment

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification of the equipment.

### **Regulatory Information**

The GE Vingmed Ultrasound product families are tested to meet all applicable requirements in relevant EU Directives and European/International standards. (See "Standards used" below.) Any changes to accessories, peripheral units or any other part of the system must be approved by the manufacturer; GE Vingmed Ultrasound. **Ignoring this advice may compromise the regulatory approvals obtained for the product.**

Please consult your local GE Vingmed Ultrasound representative for further details.

### Standards used

Our ultrasound scanners are class I devices, according to Clause 14 of IEC 60601-1 (1988).

To fulfill the requirements of relevant EC directives and/or European Harmonized/International standards, the following documents/standards have been used:

| STANDARD/DIRECTIVE                                         | SCOPE                                                                                                                                                                                                                                                         |

|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 93/42/EEC                                                  | Medical Devices Directive (MDD)                                                                                                                                                                                                                               |

| IEC 801-2/ 4.1991                                          | Electrostatic Discharge                                                                                                                                                                                                                                       |

| IEC 801-3/ 1984                                            | Radiated Electromagnetic Field                                                                                                                                                                                                                                |

| IEC 801-4/ 1988                                            | Electrical Fast Transient/Burst                                                                                                                                                                                                                               |

| IEC 801-5/ 1.1993(draft)                                   | Surge                                                                                                                                                                                                                                                         |

| EN 55011/CISPR 11/ 3.1991                                  | Emitted noise according to Class B requirements + Electromagnetic Suscep-<br>tibility                                                                                                                                                                         |

| IEC 60601-1 (1988)<br>EN 60601-1/ 1990<br>UL2601-1/ 8.1994 | Medical Electrical Equipment, Part 1; General Requirements for Safety<br>"CLASSIFIED BY UNDERWRITERS LABORATARIES INC WITH RE-<br>SPECT TO ELECTRICAL SHOCK, FIRE AND MECHANICAL HAZ-<br>ARDS ONLY IN ACCORDANCE WITH UL2601-1 AND CAN/CSA<br>C22.2 NO.601.1" |

| IEC 1157/ EN 61157/ 1994                                   | Requirements for the declaration of the acoustic output of medical diagnos-<br>tic ultrasonic equipment.                                                                                                                                                      |

| IEC EN 60601-1-2/1993                                      | Medical Electrical Equipment - part 2. Collateral standard: Electromagnetic compatibility - Requirements and tests.                                                                                                                                           |

NOTE:

.

1) Any rest energy within our scanners or their components will be below 60V DC or 2 mJ.

### 2 About This Manual

#### 2.1 Abstract

The purpose of this manual is to provide information which will enable the technician to diagnose and repair most problems encountered in the use of System FiVe. It is not a guide to operation. Information pertaining to this is found in the System FiVe User Manual.

The manual is not intended to be used for troubleshooting on board level. This will be done on the factory. Some of the modules in the System FiVe are older designs, thus occasionally signal names on the module might not be the same on another module, even though the signal is the same. This is done to ease troubleshooting on board level at the factory.

#### 2.2 Overview

The service manual is divided into several main chapters:

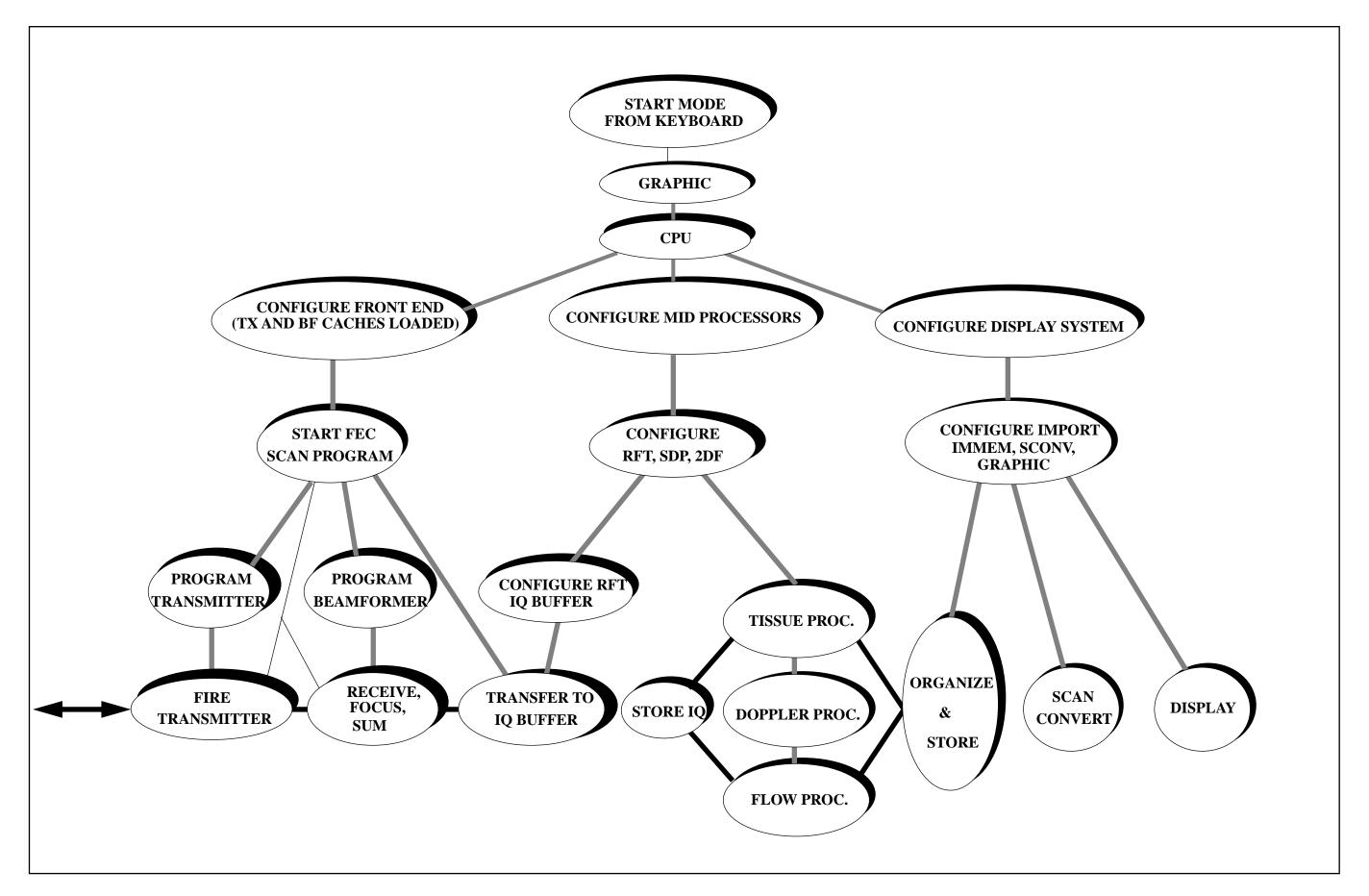

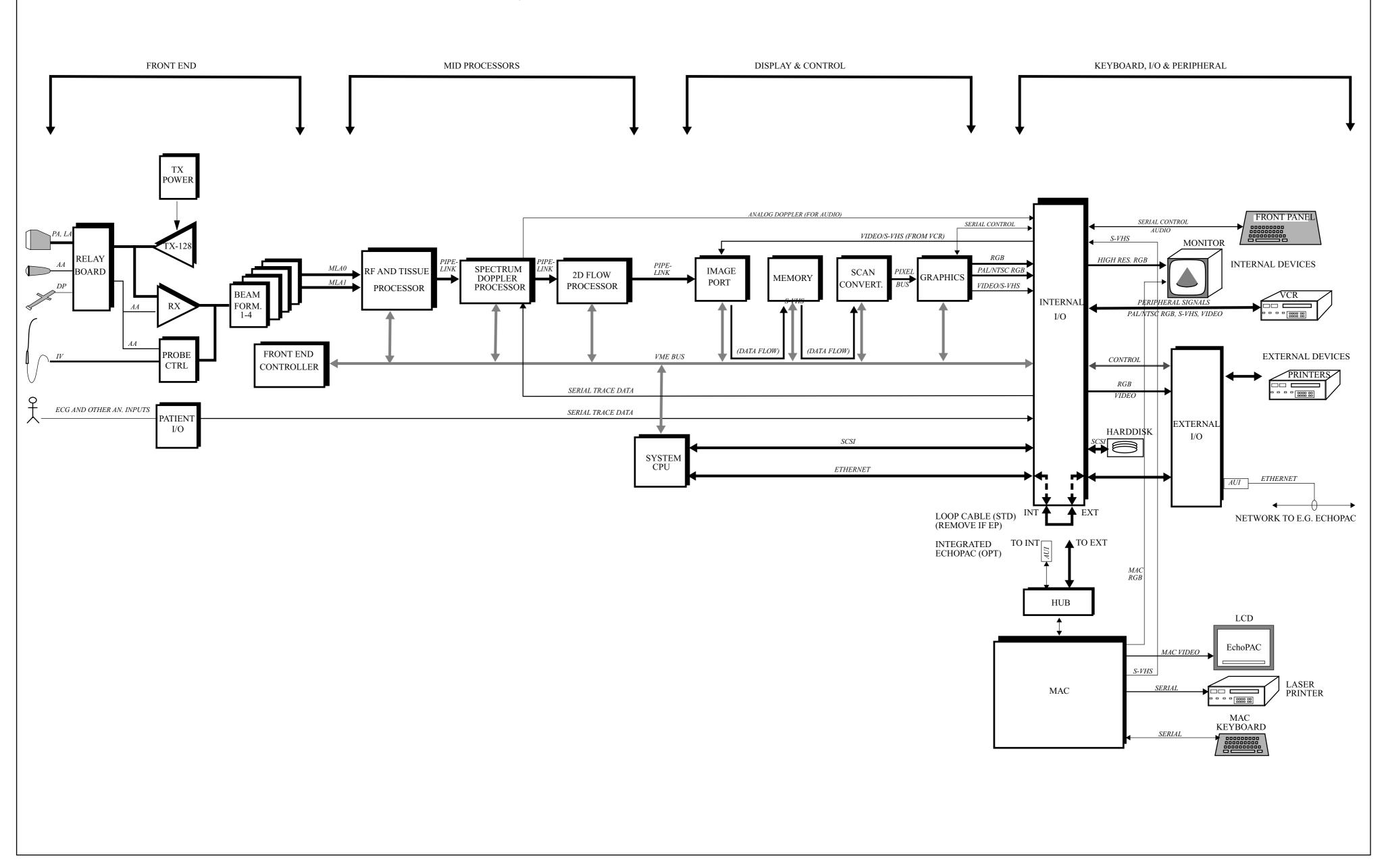

- The Theory of Operation chapter consists of two major sections; a <u>Principles of</u> <u>Operation</u> section which gives a lesson in the basics of ultrasound, and a <u>System</u> (and subsystem) <u>Description</u> section detailing how the system works, down to board level.

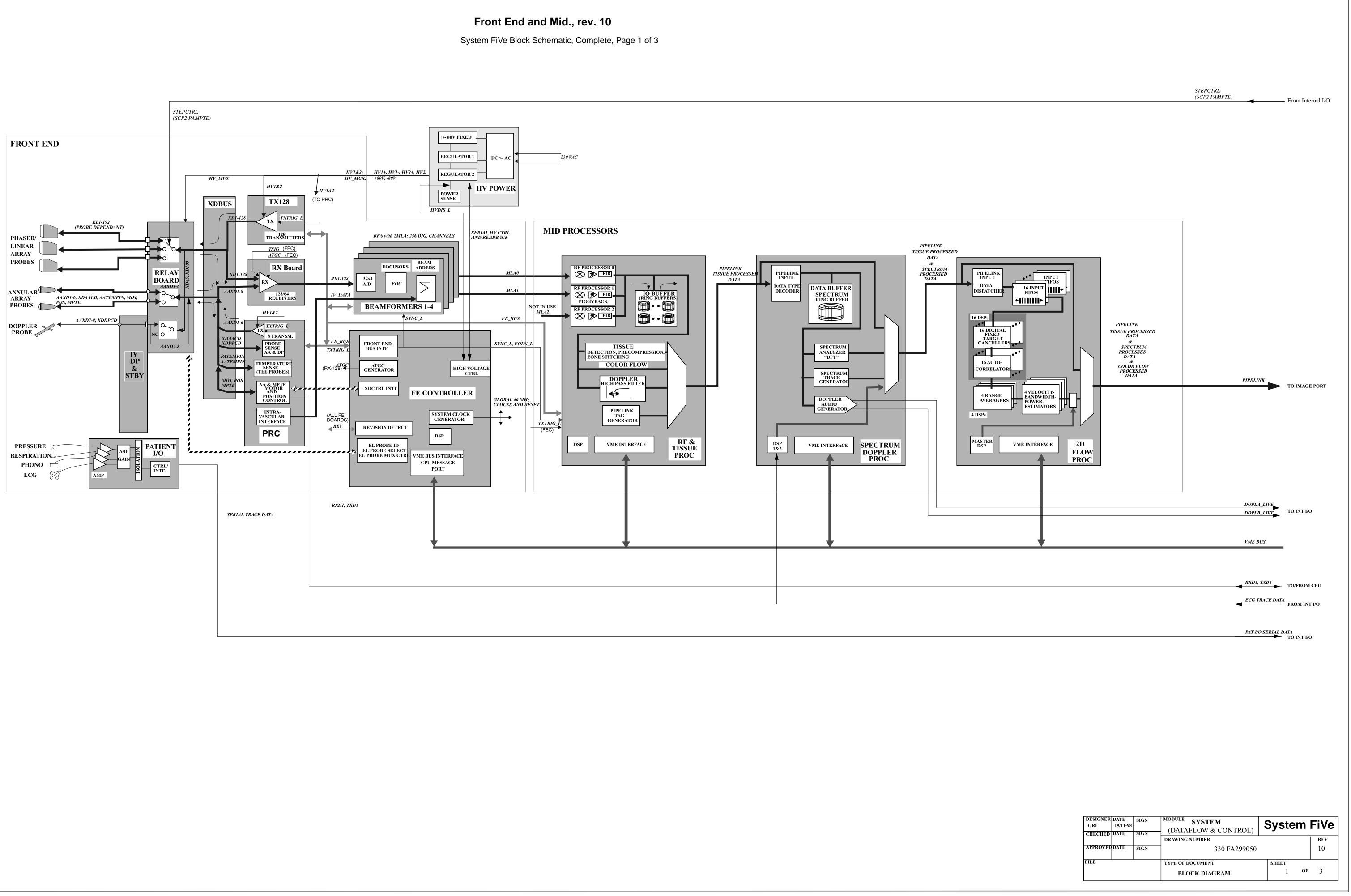

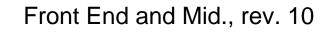

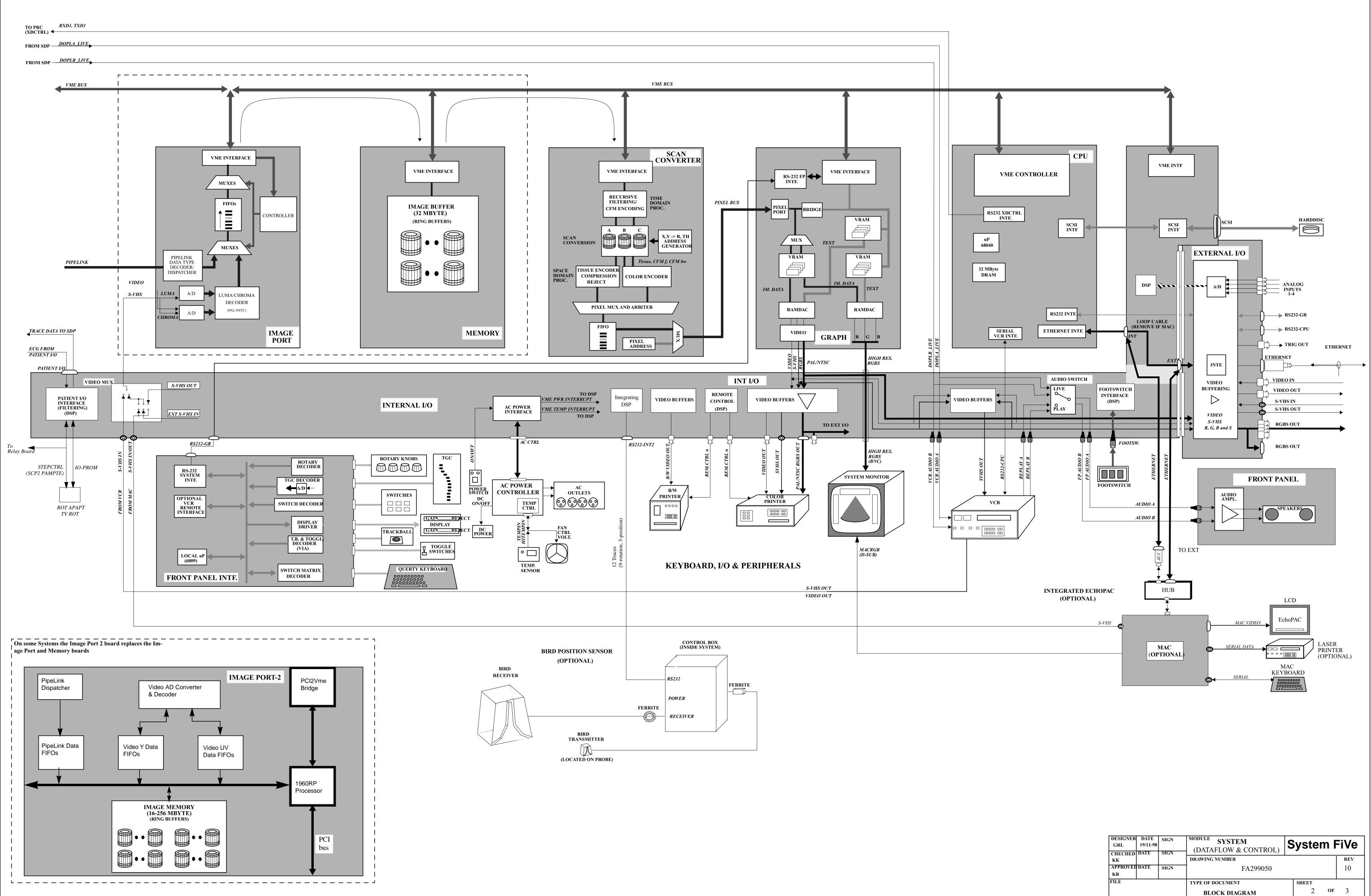

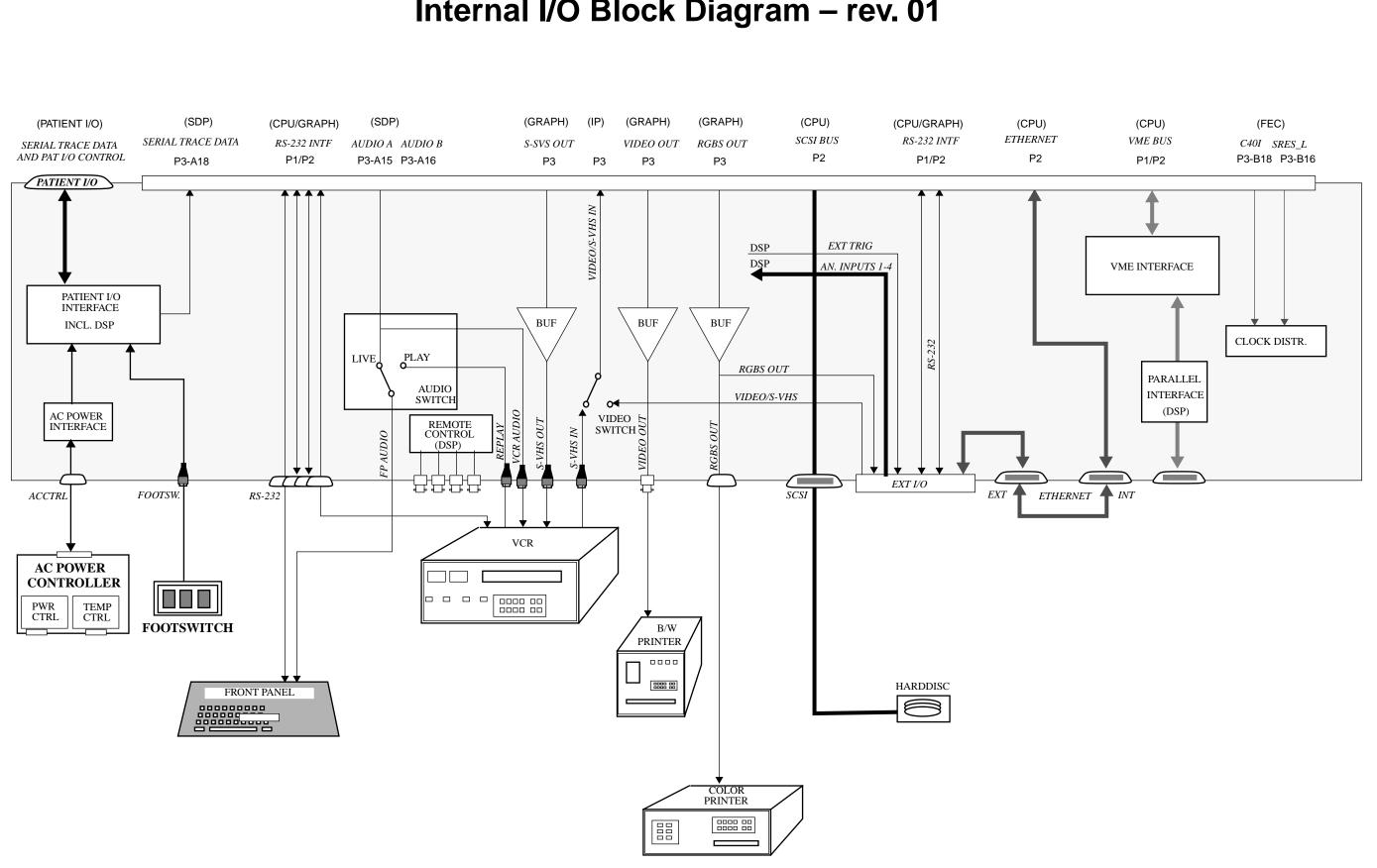

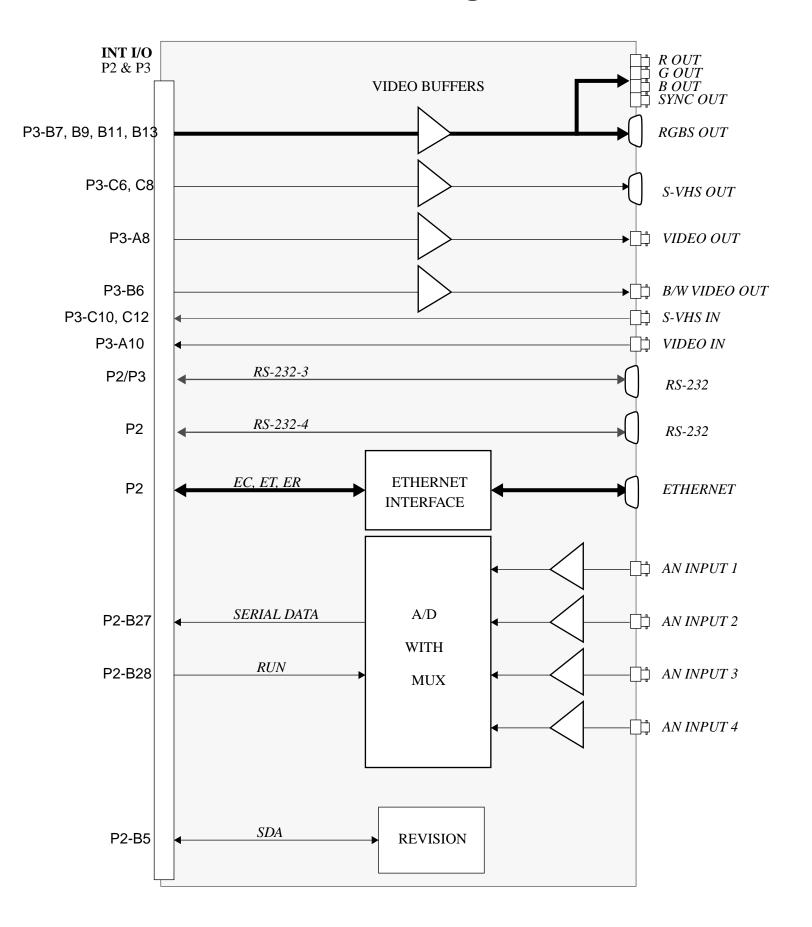

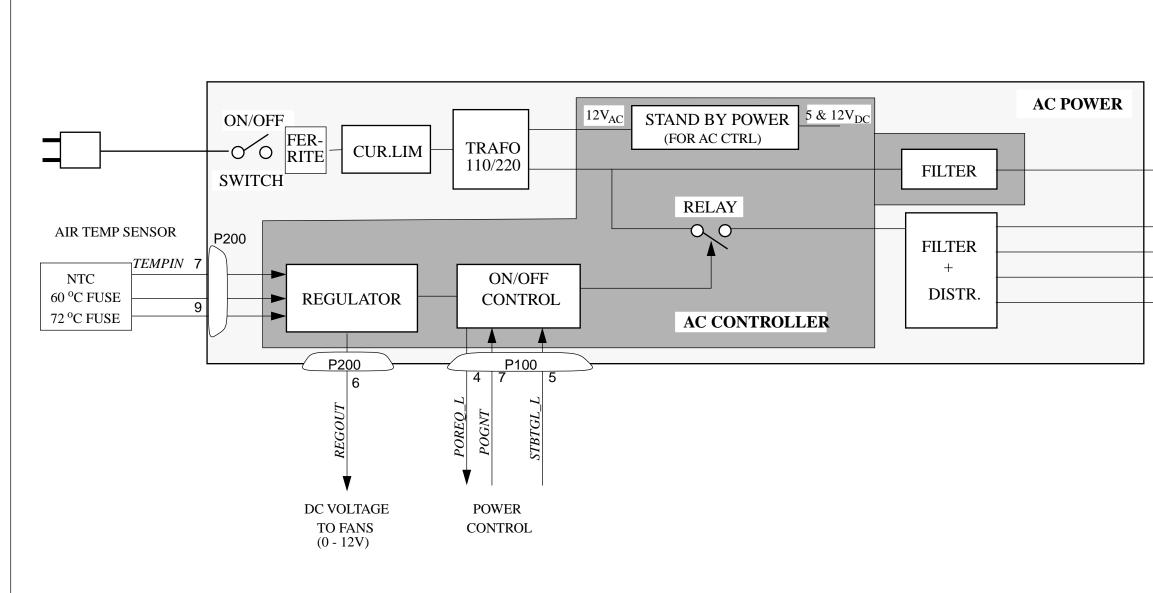

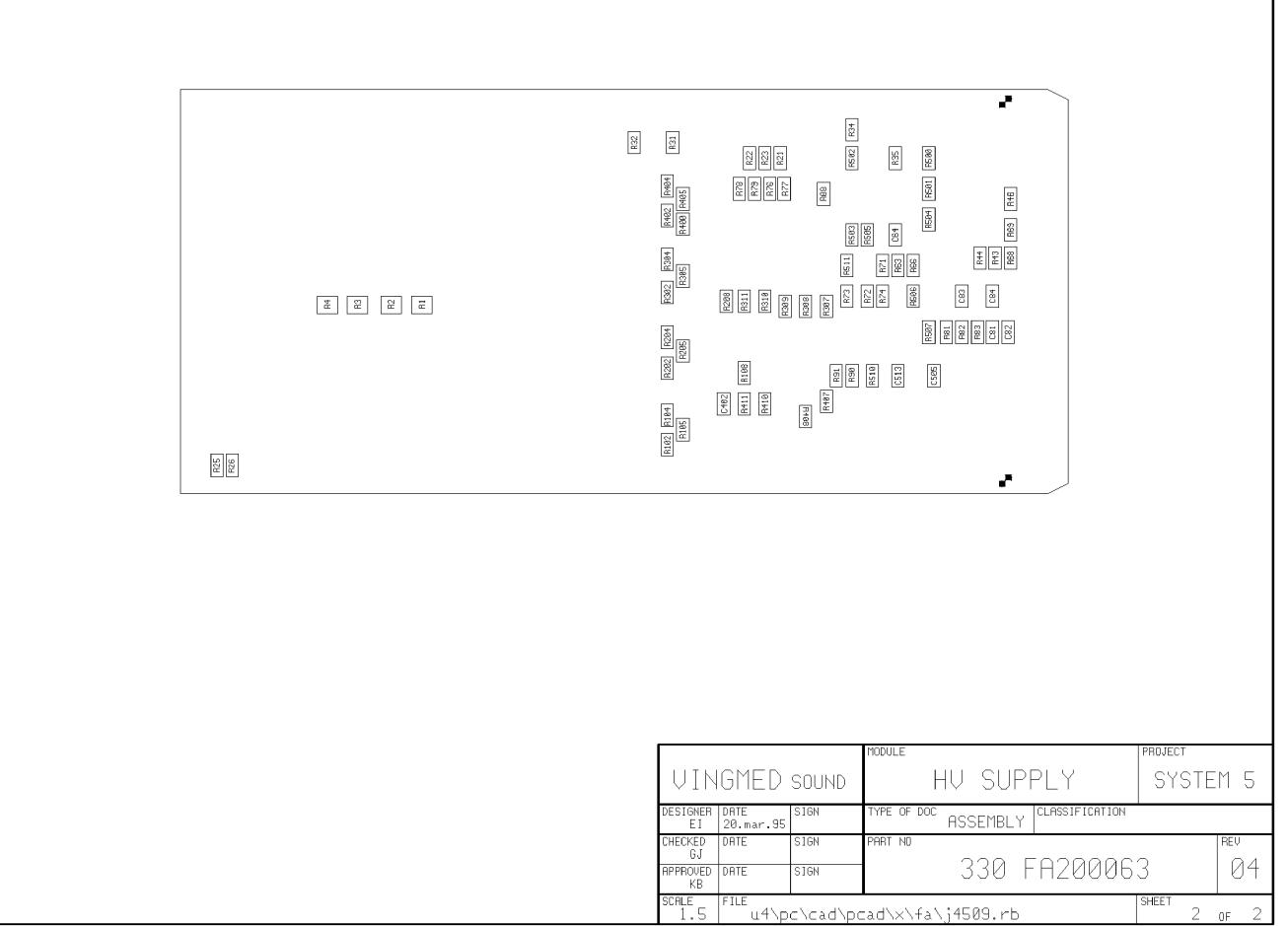

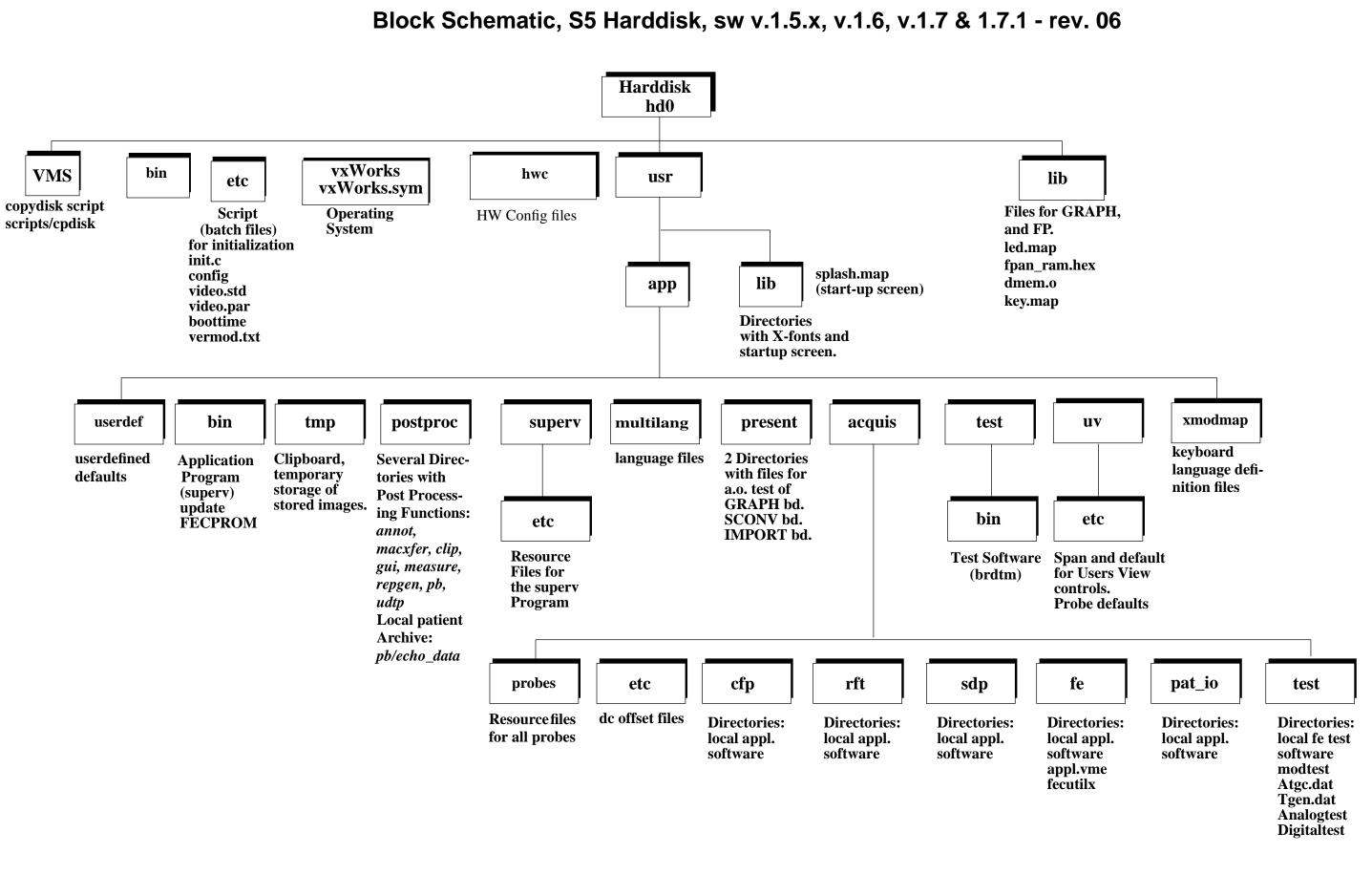

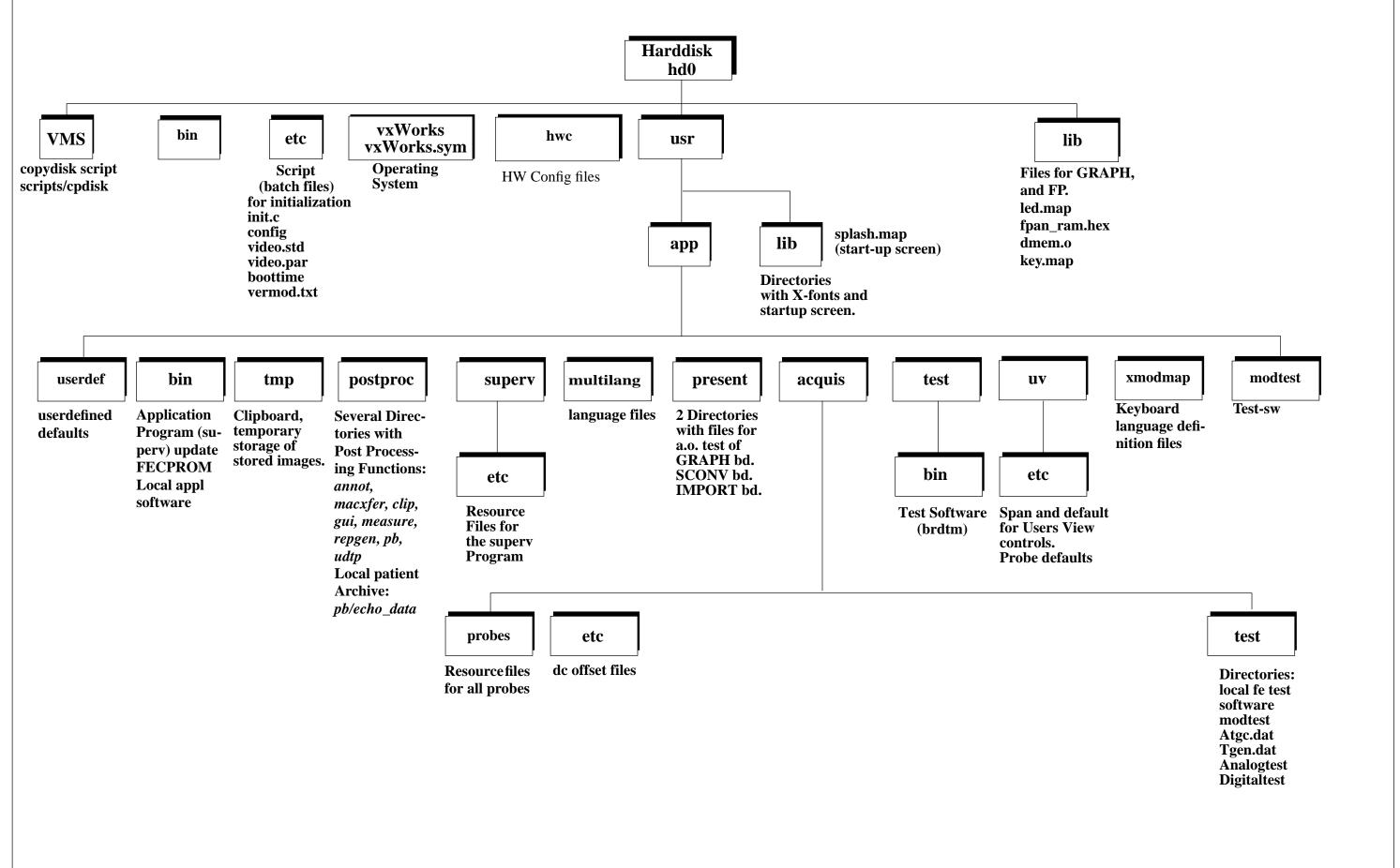

- The Block Schematics chapter contains all block schematics for the system, the boards and other assemblies. They are all referenced in the Descriptions section of the Theory of Operation chapter.

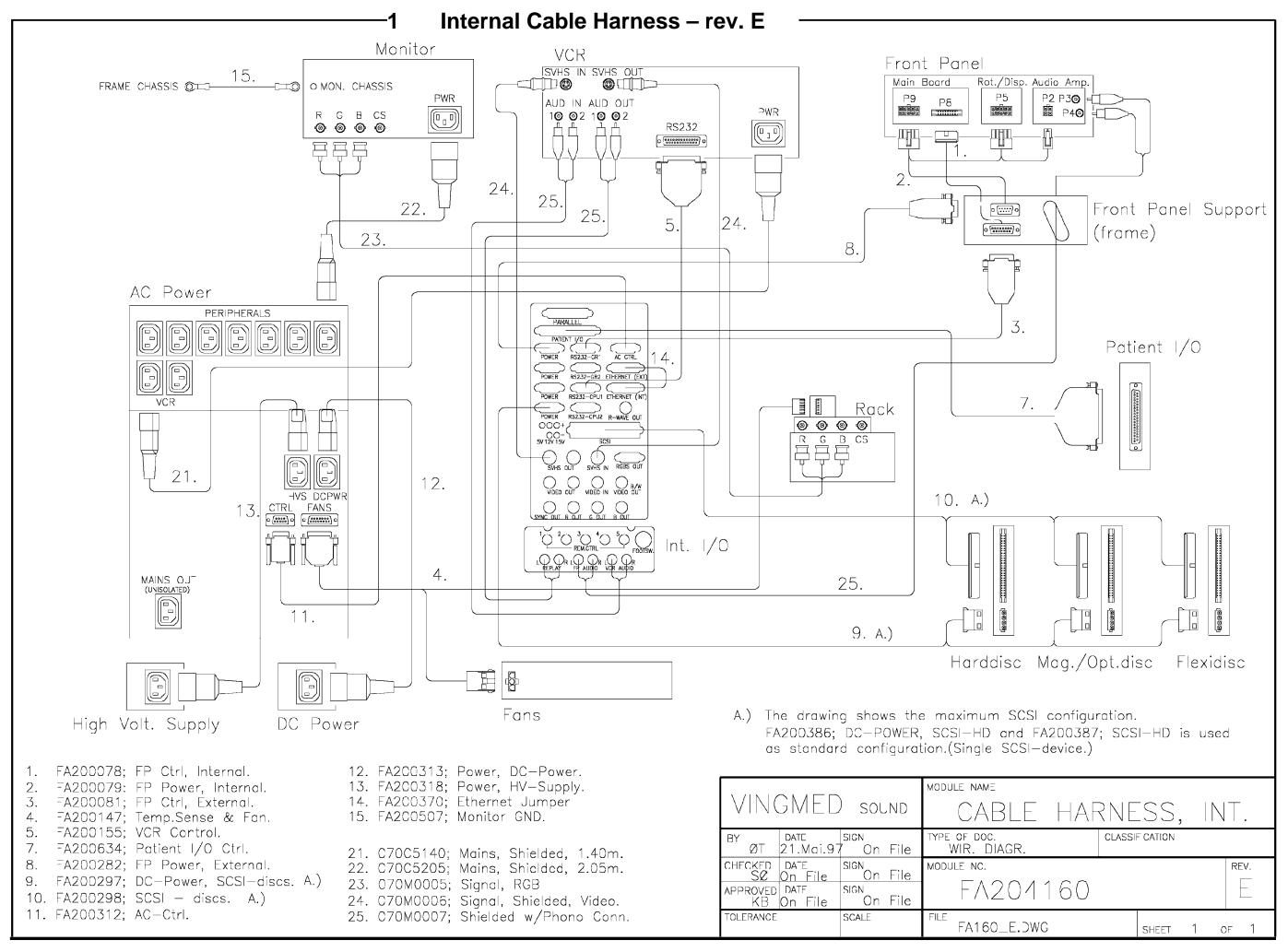

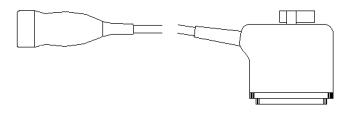

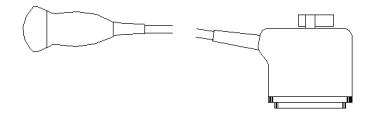

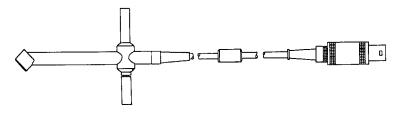

- The Cables chapter contains drawings and signal lists of cables within the system.

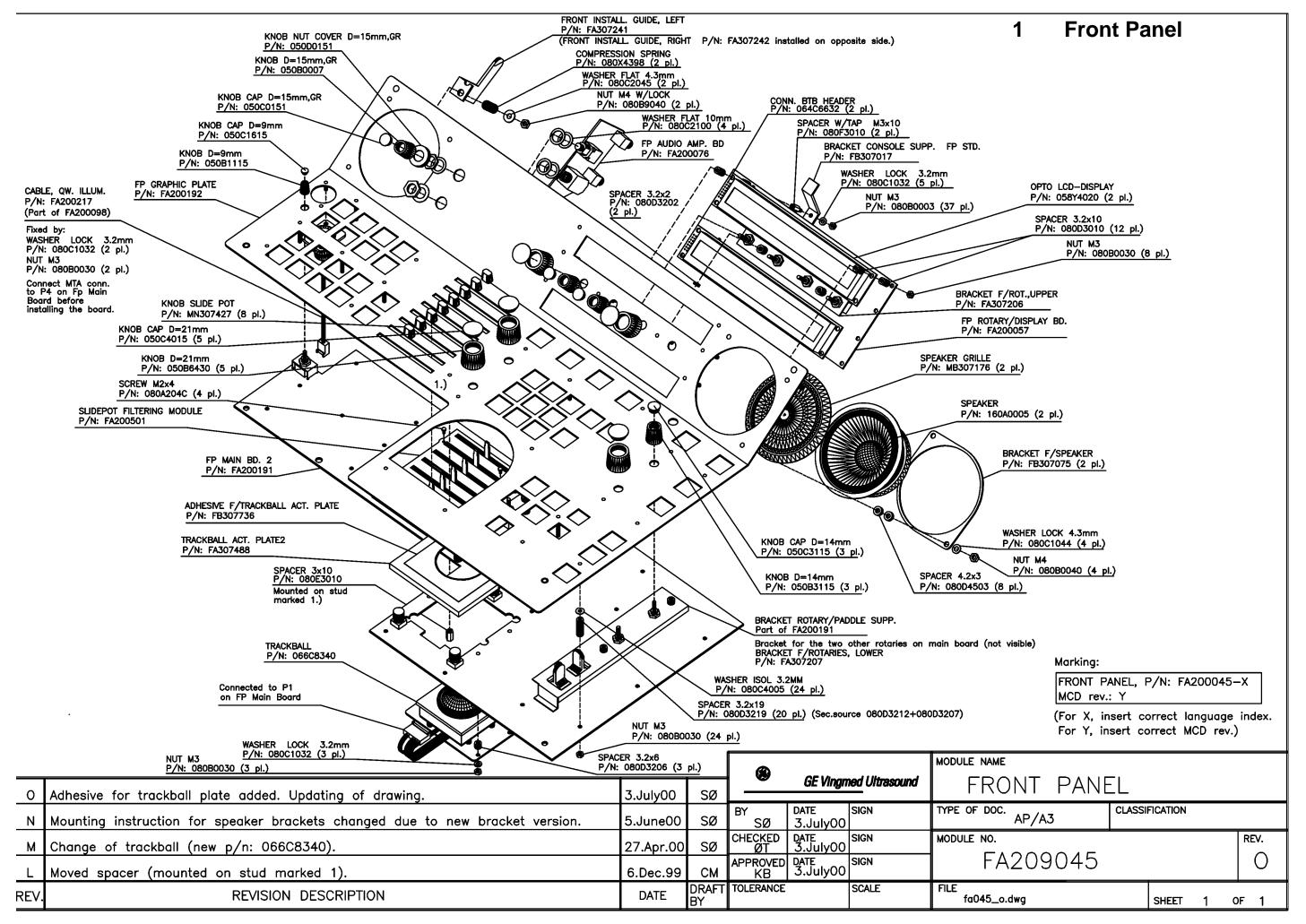

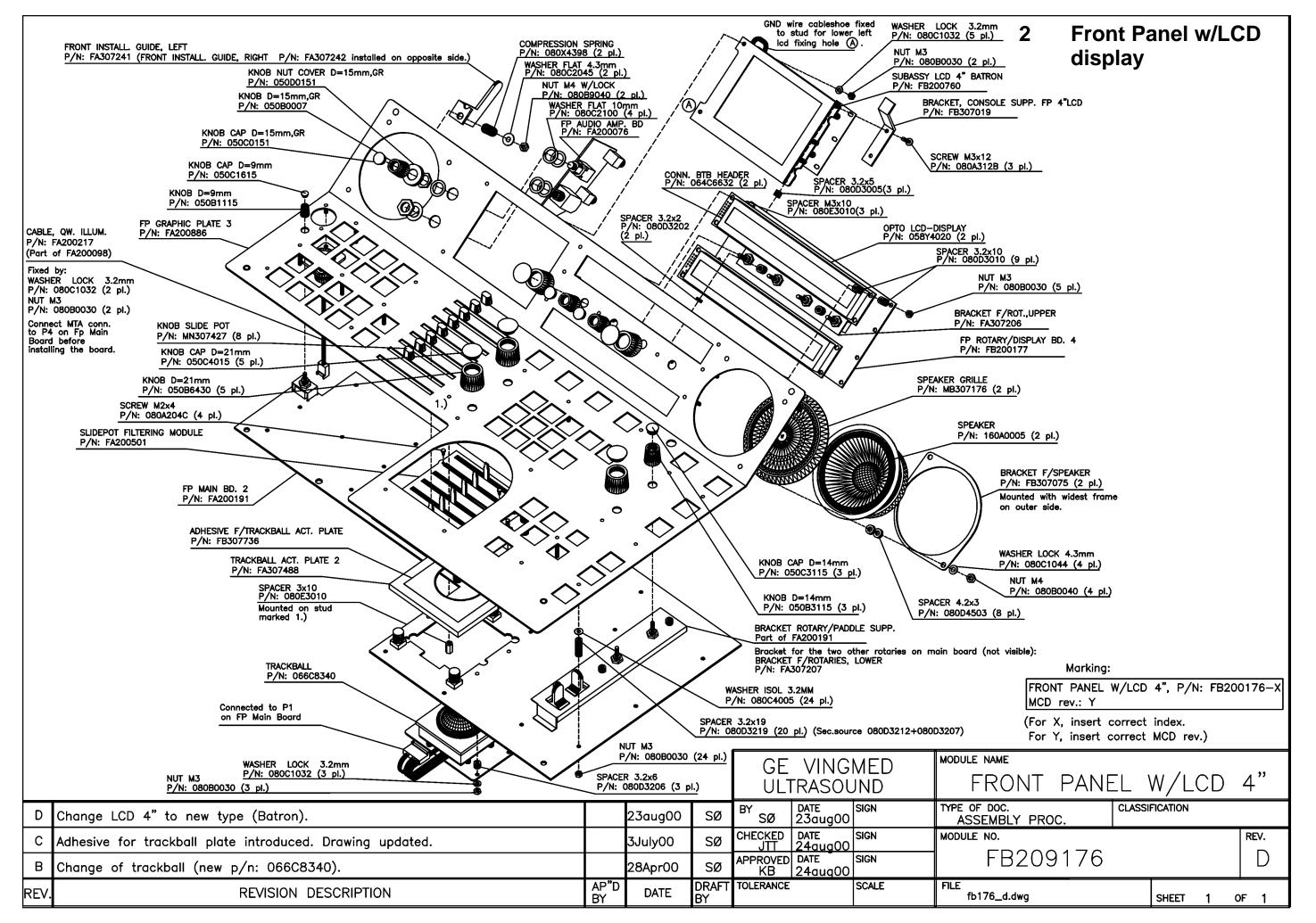

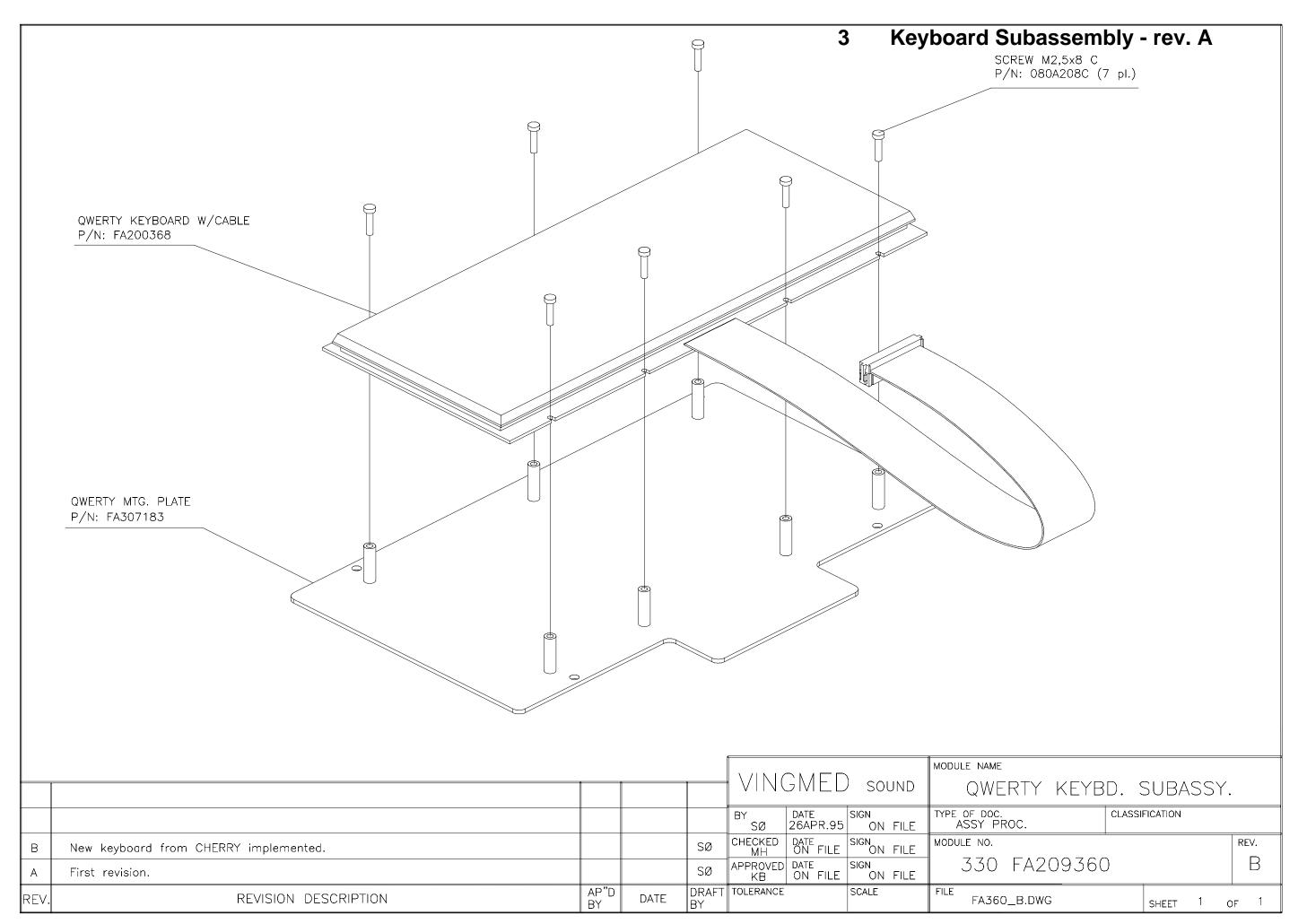

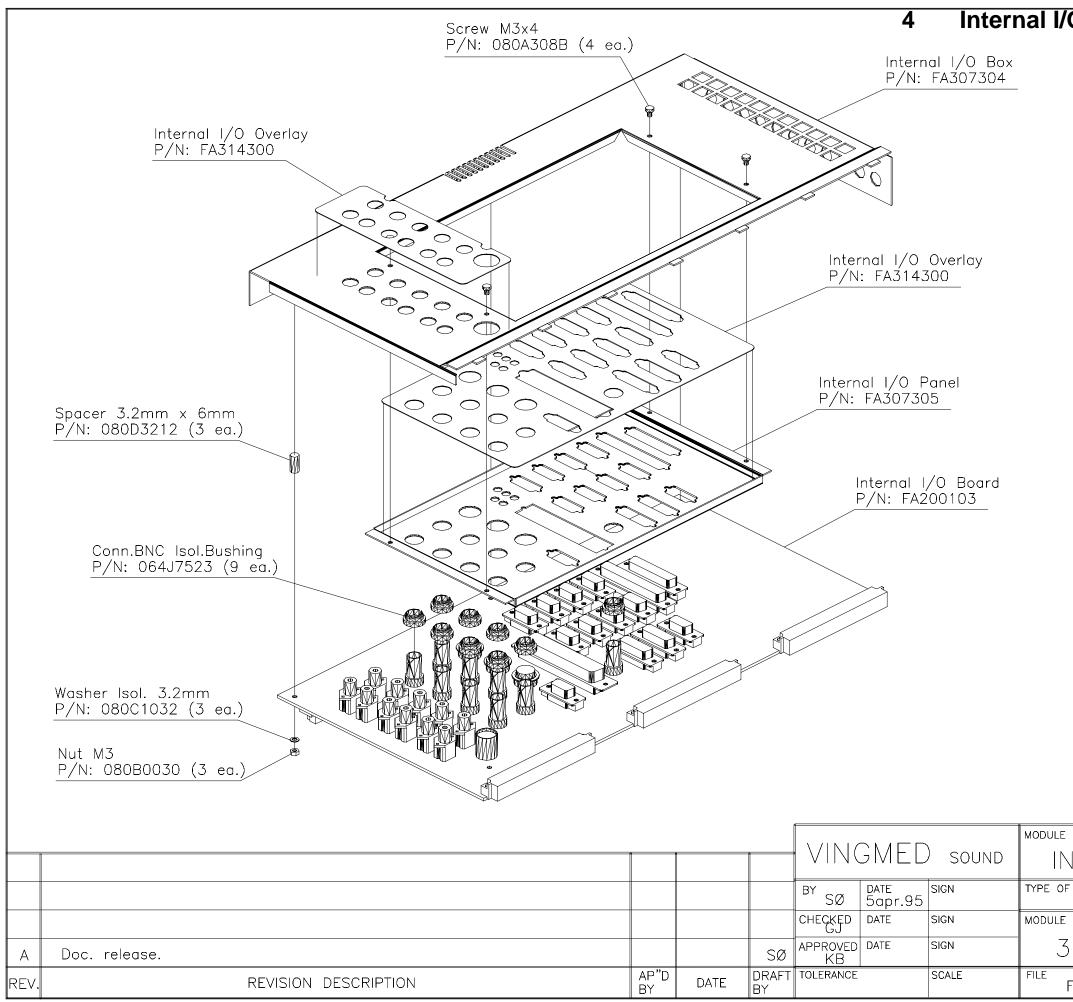

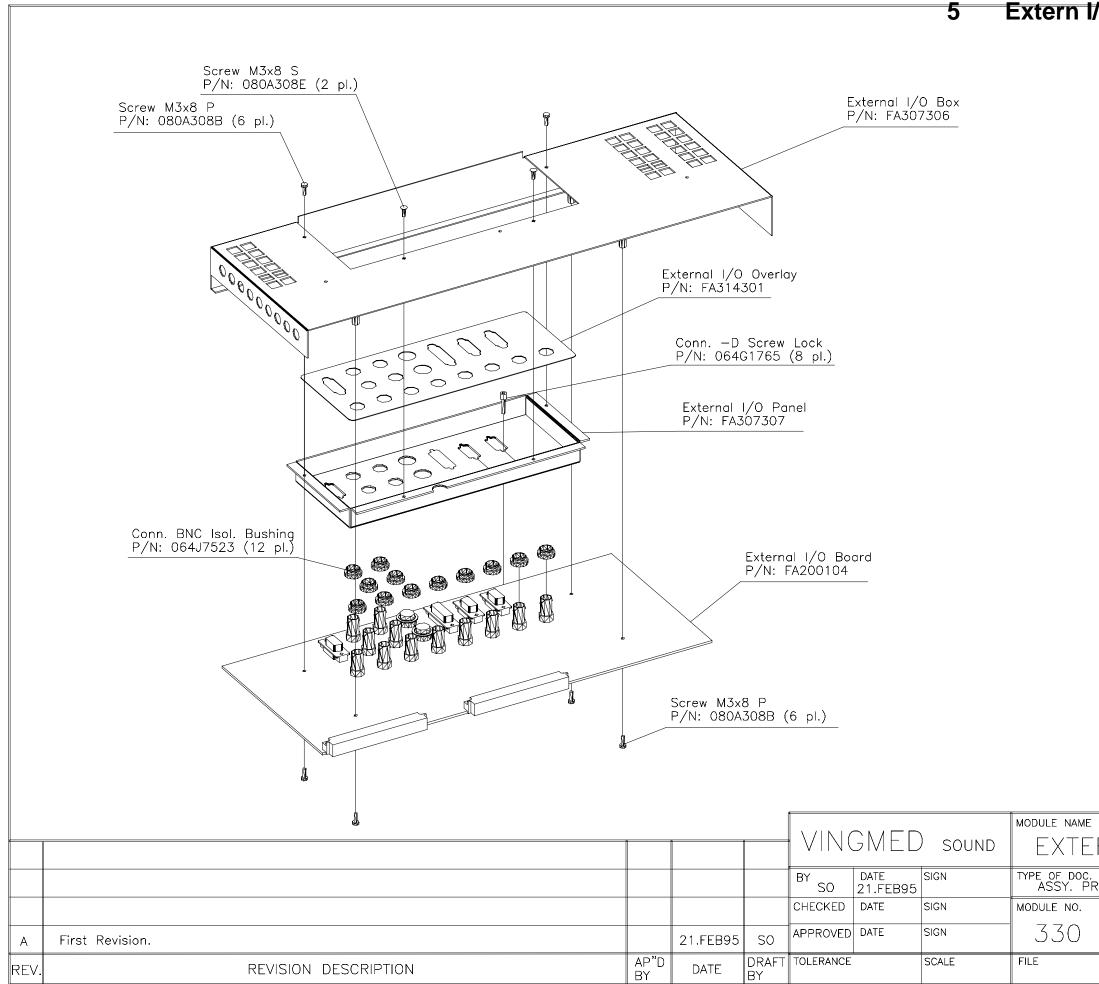

- The Mechanical Subassemblies chapter gives exploded view drawings.

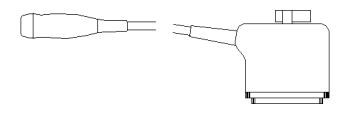

- The Probes chapter includes a listing of all System FiVe probes; types, frequencies, color codes etc.

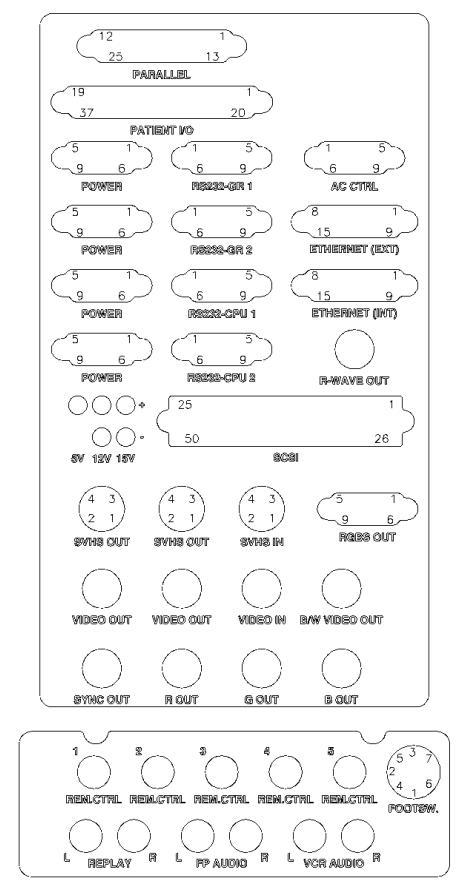

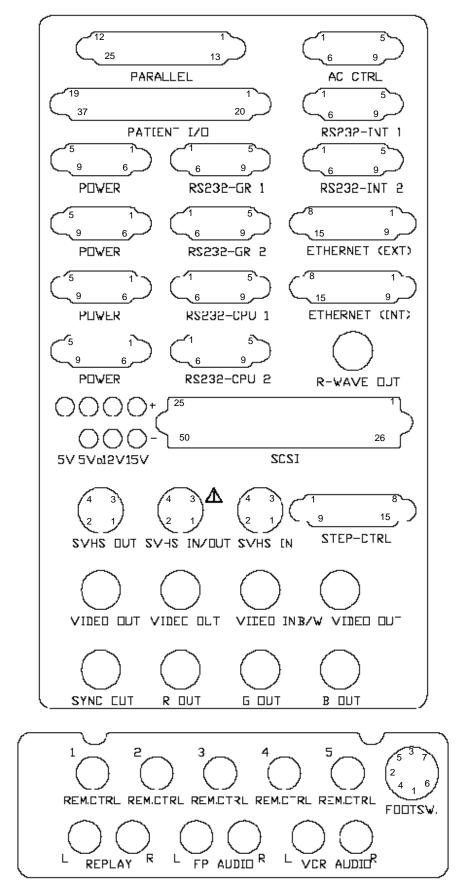

- The I/O Signals lists signal names and technical data for the I/O signals.

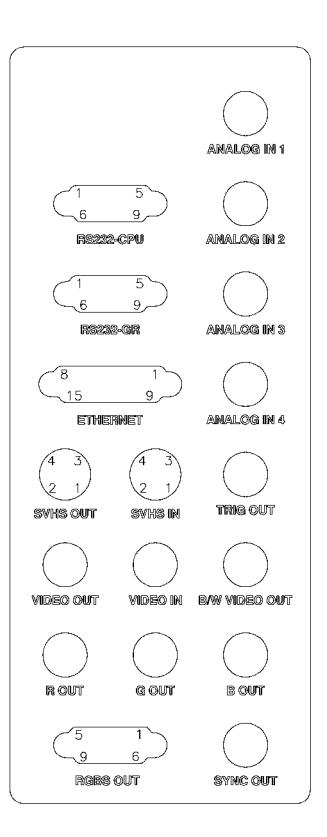

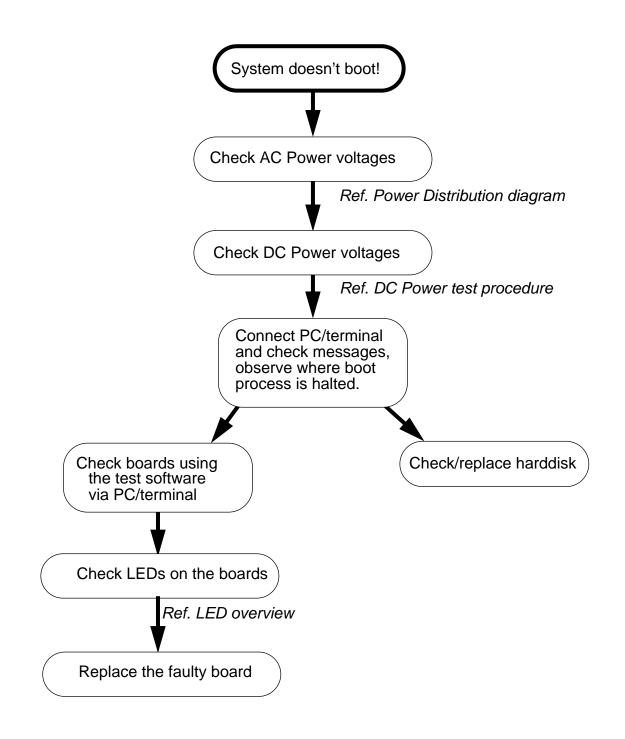

- The Troubleshooting Guide chapter is an aid in the process of diagnosing problems, and gives guidance for most types of errors.

- The Configurations chapter lists the different software and hardware revisions on the subassemblies, and links them to a system level revision and/or software version.

- The Maintenance Procedures and Replacement Procedures chapter also gives you installations procedures for e.g. software upgrades.

- The Peripherals chapter contains all necessary information required to install any peripheral listed in the beginning of the section; location, power connection, signal interface, user setup, switch settings etc.

- The Part Number List chapter lists all part numbers on all assemblies and subassemblies likely to be replaced.

#### 2.3 How to Use the Manual Effectively

In order to use the manual effectively, it is essential that you have read or at least browsed through the whole book. When using the manual for troubleshooting, the following sequence should be followed.

- 1. Characterize the fault symptoms as specifically as possible.

- 2. Use the troubleshooting guide as a reference, and try and isolate the problem down to board level if possible. The guide will have references to other parts of the manual. In most cases fault isolation would imply running a test software routine.

Note: One part of the diagnostic software will be accessible for the user.

3. Replace the indicated part(s).

#### 2.4 Technical Skills Required

The manual is intended for use by qualified technical personnel with knowledge and experience in servicing advanced medical instrumentation. The reader should have basic electronic knowledge, and should have an understanding of techniques generally used in troubleshooting and repair. As mentioned before, a System FiVe Training Seminar is a requirement for servicing the equipment.

#### 2.5 Repair

No printed circuit boards nor power supplies must be repaired in the field. All such parts must be returned to the manufacturer, GE Vingmed Ultrasound, Norway for repair.

### 3 Test Equipment and Tools Required

#### 3.1 General Tools

This is a list of the minimum required tools for service on GE Vingmed Ultrasound's products

- PC Laptop with MS Windows 95 or MS NT 4

- Minimum 200 MB free disk space

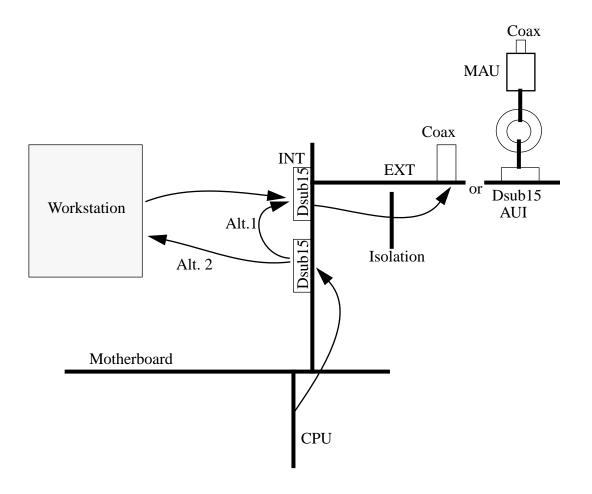

- Ethernet adapter

- CD-ROM

- RS-232 Cable (crossed)

- Twisted Pair Ethernet Cable (crossed)

- Twisted Pair Transceiver (MAU)

- Service Floppy Disks

- Service MO-Disk, 1.3 GB

- Phillips Screw Drivers

- Flat screw drivers

- Box spanners

- Allen keys

- Oscilloscope

- Multimeter

- Service Manuals

- Anti static mat / wrist band

- IC removers

- Antistatic brush for PCBs

- APA Probe cable

- APA Probe (optional)

- PA Probe (optional)

- Macintosh Keyboard

- Macintosh Mouse

- USB to ADB converter

- Multi-voltage SCSI CD ROM drive from Apple

- SCSI cable for CD-ROM Drive/Mac

- Power Cable for Multi-voltage SCSI CD ROM drive

- Simple External Video Grabber Board (optional)

#### 3.2 Tools, Mobility Kit (Changing Wheels)

(In addition to the tools above):

• Sax jack, GEVU Part Number: 098C0001

- Tri-pod stand (2x), GEVU Part Number: 098C0010

- Umbrako wrench, 5 mm (front wheels)

- Umbrako wrench, 6 mm (rear wheels)

Your Notes:

### 4 New Functions/ Features

#### 4.1 Abstract

The purpose of this document is to give a listing of the system features/functions that are supported by the different software versions:

### 4.2 Document History

| Rev. | Date          | Ву  | Description                                                  |

|------|---------------|-----|--------------------------------------------------------------|

| 01   | 1 Aug 1996    | GRL | First version of document per V1.1 release                   |

| 02   | 30 Apr 1997   | GRL | Updated per V1.2 release.                                    |

| 03   | 17 Nov 1997   | GRL | Updated per V1.3 release.                                    |

| 04   | 10 Jun 1998   | GRL | Updated per V1.4 release                                     |

| 05   | 11 Nov 1998   | GRL | Updated per V1.5 release                                     |

| 06   | 28 Feb 1999   | LHS | Updated per V1.5.3 & V1.6 release                            |

| 07   | 6 Aug 1999    | LHS | Updated per V1.7 release                                     |

| 08   | 10 Sep 1999   | LHS | Updated per V1.8 release                                     |

| 09   | 19. Nov. 1999 | LHS | Included info for sw v.1.7.1. Support for new TX128-2 Board. |

| 10   | 2. Dec. 1999  | LHS | Included info for sw. v.1.9.                                 |

| 11   | 1. Oct. 2000  | LHS | Included info for sw. v.1.9.x                                |

### 4.3 Supported Features

Please see the table starting on page "Intro-13".

#### Macintosh HD:User:James: @i-arb:Service:S5\_ServiceMan:S5\_serv\_files:04\_features\_b\_11.fm. Printed: December 5, 2000.

| svstem]f][\ |

|-------------|

| E           |

| Service     |

| Š           |

| lanı        |

| Manual,     |

|             |

| 091         |

| FA091050 r  |

| )<br>rej    |

| <u>~</u>    |

|             |

| Feature                 | Comments                  | V1.0 | V1.1 | V1.2 | V1.3 | V1.4 | V1.5 | V1.5.3 | V1.6                               | V1.7/<br>1.7.1                     | V1.8                               | V1.9                               | V<br>1.9.x                         |

|-------------------------|---------------------------|------|------|------|------|------|------|--------|------------------------------------|------------------------------------|------------------------------------|------------------------------------|------------------------------------|

| 2D                      |                           |      |      |      |      |      |      |        |                                    |                                    |                                    |                                    |                                    |

| Zoom                    |                           |      | x    | x    | х    | x    | х    | x      | x                                  | x                                  | x                                  | x                                  | x                                  |

| Compound                | LA probes on Premium only | х    | x    | x    | х    | x    | x    | x      | x                                  | x                                  | х                                  | x                                  | x                                  |

| RF imaging              |                           |      |      | Opt. | Opt. | Opt. | Opt. | Opt.   | Opt.                               | Opt.                               | Opt.                               | Opt.                               | Opt.                               |

| Contrast imaging        | With contrast agents      |      |      | Opt. | Opt. | Opt. | Opt. | Opt.   | Opt.                               | Opt.                               | Opt.                               | Opt.                               | Opt.                               |

| Octave Imaging          | Certain probes only       |      |      | Opt. | х    | х    | х    | х      | х                                  | х                                  | x                                  | х                                  | х                                  |

| Color Flow              |                           |      |      | !    |      | 1    | !    | !      | !                                  |                                    | 1                                  |                                    |                                    |

| Zoom                    |                           |      | x    | x    | х    | x    | x    | x      | x                                  | x                                  | x                                  | x                                  | x                                  |

| TVI                     | Tissue Velocity Imaging   |      | x    | x    | x    | x    | x    | x      | x<br>Opt.<br>on<br>"Adva<br>ntage" | x<br>Opt.<br>on<br>"Adva<br>ntage" | x<br>Opt.<br>on<br>"Adva<br>ntage" | x<br>Opt.<br>on<br>"Adva<br>ntage" | x<br>Opt.<br>on<br>"Adva<br>ntage" |

| Angio                   |                           |      | x    | x    | х    | x    | x    | x      | x                                  | x                                  | x                                  | x                                  | x                                  |

| Velocity Profiles       |                           |      |      | x    | х    | x    | x    | x      | x                                  | x                                  | x                                  | x                                  | x                                  |

| Anatomic Color M-Mode   |                           |      |      | x    | х    | x    | x    | x      | x                                  | x                                  | x                                  | x                                  | x                                  |

| Mosaic ("HP") color map |                           |      |      |      |      |      | x    | x      | x                                  | x                                  | x                                  | x                                  | x                                  |

| M-Mode                  |                           |      |      |      |      |      |      |        |                                    |                                    |                                    |                                    |                                    |

| Anatomic M-Mode         |                           |      |      | x    | х    | x    | x    | x      | x                                  | x                                  | x                                  | x                                  | x                                  |

| Doppler                 |                           |      |      | •    | -    |      | •    | •      |                                    |                                    |                                    |                                    |                                    |

| Tracking Doppler        | Only on Premium systems   | х    | x    | x    | х    | x    | х    | х      | x                                  | x                                  | x                                  | x                                  | x                                  |

| Autotrace               |                           |      |      | x    | х    | x    | x    | x      | x                                  | x                                  | x                                  | x                                  | x                                  |

| Feature                       | Comments                                                   | V1.0 | V1.1 | V1.2 | V1.3 | V1.4 | V1.5 | V1.5.3 | V1.6 | V1.7/<br>1.7.1 | V1.8 | V1.9 | V<br>1.9.x |

|-------------------------------|------------------------------------------------------------|------|------|------|------|------|------|--------|------|----------------|------|------|------------|

| Different Doppler color maps  | Red, blue, yellow, gray, black on white                    |      |      |      |      | x    | x    | x      | х    | x              | x    | x    | x          |

| M&A                           |                                                            | I    |      | 1    |      | 1    |      |        |      | 1              |      |      |            |

| Cardiac                       |                                                            | x    | x    | x    | x    | x    | x    | x      | х    | x              | x    | x    | x          |

| PV                            |                                                            |      | x    | x    | x    | x    | x    | x      | х    | x              | x    | x    | x          |

| Abdominal                     |                                                            |      |      | х    | х    | х    | х    | x      | х    | х              | х    | х    | х          |

| Ob/gyn.                       |                                                            |      |      |      |      |      |      |        |      |                |      |      |            |

| EchoPAC                       |                                                            | I    |      |      |      |      |      |        |      |                |      |      |            |

| EchoPAC support               |                                                            | x    | x    | Opt. | Opt. | Opt. | Opt. | Opt.   | Opt. | Opt.           | Opt. | Opt. | Opt.       |

| 24 bit frame grabbing         |                                                            |      |      | Opt. | Opt. | Opt. | Opt. | Opt.   | Opt. | Opt.           | Opt. | Opt. | Opt.       |

| Integrated EP support         |                                                            |      |      | Opt. | Opt. | Opt. | Opt. | Opt.   | Opt. | Opt.           | Opt. | Opt. | Opt.       |

| EchoPAC 3D support            |                                                            |      |      | Opt. | Opt. | Opt. | Opt. | Opt.   | Opt. | Opt.           | Opt. | Opt. | Opt.       |

| Continuous Capture support    | Including Frame Grabber<br>III and RGB/S-VHS switch<br>box |      |      |      |      |      | Opt. | Opt.   | Opt. | Opt.           | Opt. | Opt. | Opt.       |

| Other:                        |                                                            | 1    |      | 1    |      | 1    | 1    |        |      | 1              | 1    | 1    |            |

| Patient archive               |                                                            |      |      | x    | x    | x    | x    | x      | х    | x              | x    | x    | x          |

| Clipboard support             |                                                            |      |      | x    | x    | x    | x    | x      | х    | x              | x    | x    | x          |

| User defined defaults         |                                                            |      |      | x    | x    | x    | х    | x      | х    | x              | x    | x    | x          |

| Annotation recall/<br>restore |                                                            |      |      |      | x    | x    | x    | x      | х    | x              | x    | x    | x          |

| Update function               |                                                            |      |      |      | x    | x    | x    | x      | х    | x              | x    | x    | x          |

| 3D acquisition                | FLA, CLA                                                   |      |      | Opt. | Opt. | Opt. | Opt. | Opt.   | Opt. | Opt.           | Opt. | Opt. | Opt.       |

| VCR remote control            |                                                            |      |      | x    | x    | x    | x    | x      | х    | x              | x    | x    | x          |

Introduction - rev. 11

GE Vingmed Ultrasound

| Feature                      | Comments | V1.0 | V1.1 | V1.2 | V1.3 | V1.4 | V1.5 | V1.5.3 | V1.6 | V1.7/<br>1.7.1 | V1.8 | V1.9 | V<br>1.9.x |

|------------------------------|----------|------|------|------|------|------|------|--------|------|----------------|------|------|------------|

| M&A on playback              |          |      |      |      | х    | x    | х    | x      | х    | х              | х    | х    | х          |

| Foot switch support          |          |      |      | х    | x    | x    | х    | х      | х    | х              | x    | x    | х          |

| 2D Frame counter             |          |      |      | х    | x    | x    | x    | x      | х    | х              | x    | x    | x          |

| Heart rate indicator         |          |      |      | x    | x    | x    | x    | x      | х    | x              | x    | x    | x          |

| ECG trigging                 |          |      |      | x    | x    | x    | x    | x      | х    | x              | x    | x    | x          |

| Stress echo (raw data)       |          |      |      | x    | x    | x    | x    | x      | х    | x              | x    | x    | x          |

| Up/down, left/right          |          |      |      | x    | x    | x    | x    | x      | х    | x              | x    | x    | x          |

| Bodymarks                    |          |      |      |      | x    | x    | x    | x      | х    | x              | x    | x    | x          |

| Biopsy Support               |          |      |      |      | x    | x    | x    | x      | х    | x              | x    | x    | x          |

| TEE temp. override<br>(43°C) |          |      |      |      | х    | х    | x    | x      | х    | x              | х    | x    | x          |

| EchoMAT support              |          |      |      |      | Opt. | Opt. | Opt. | Opt.   | Opt. | Opt.           | Opt. | Opt. | Opt.       |

| Selectable phono filters     |          |      |      |      |      | x    | х    | x      | х    | х              | x    | x    | х          |

GE Vingmed Ultrasound

Introduction - rev. 11

Your Notes:

GE Vingmed Ultrasound

### **Table of Contents**

|                           | Chapter           | Description                                 | Page #    |

|---------------------------|-------------------|---------------------------------------------|-----------|

| The Service Man           | ual               |                                             |           |

| Introduction - rev.<br>11 | <b>1.0</b><br>1.1 | Warnings and Cautions.                      |           |

|                           | 1.2               | Electric Shock Hazard                       |           |

|                           | 1.3               | Dangerous Procedure Warnings                |           |

|                           | 1.4               | Explosion Warning                           | . Intro-5 |

|                           | 1.5               | Electrostatic Discharge Warning             | . Intro-5 |

|                           | 1.6               | Do not substitute parts or modify equipment | . Intro-6 |

|                           | <b>2.0</b><br>2.1 | About This Manual                           |           |

|                           | 2.2               | Overview                                    | . Intro-7 |

|                           | 2.3               | How to Use the Manual Effectively           | . Intro-8 |

#### **Theory of Operation**

2.4

2.5

3.0

3.1 3.2

4.0

4.1

4.2

4.3

#### System Overview

| Principles of Oper-<br>ation – rev. 06 | <b>1.0</b><br>1.1 | Introduction                                                  |         |

|----------------------------------------|-------------------|---------------------------------------------------------------|---------|

|                                        | 1.2               | Overview                                                      | . A1-3  |

|                                        | 1.3               | Revision History                                              | . A1-3  |

|                                        | 1.4               | Terminology                                                   | . A1-3  |

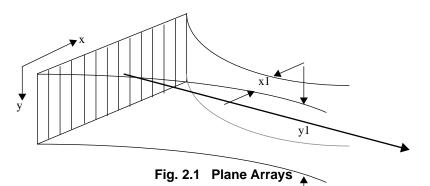

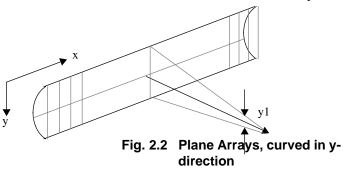

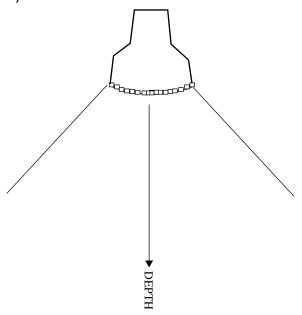

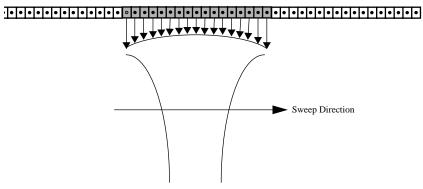

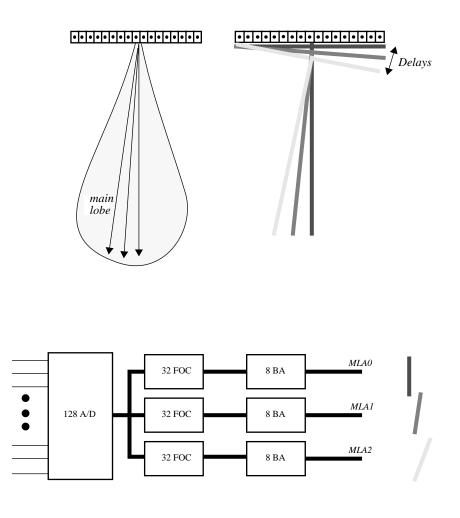

|                                        | <b>2.0</b><br>2.1 | Phased-, Linear- and Curved Linear Array Imaging Introduction |         |

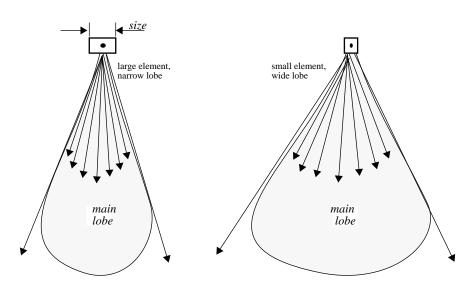

|                                        | 2.2               | Array Types                                                   | . A1-5  |

|                                        | 2.3               | Image Formats.                                                | . A1-6  |

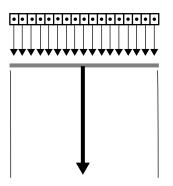

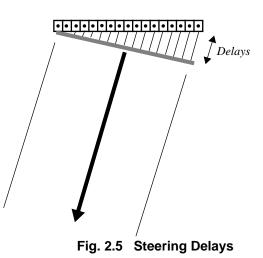

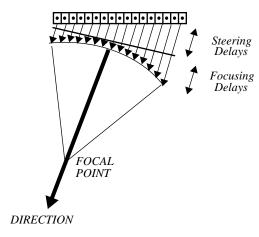

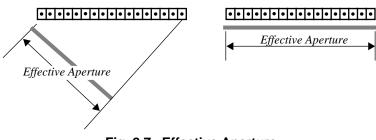

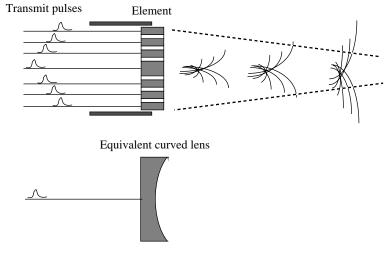

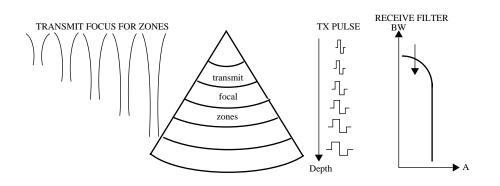

|                                        | 2.4               | Electronic Steering of Probe / Transmit Focusing              | . A1-9  |

|                                        | <b>3.0</b><br>3.1 | Annular Array Imaging                                         |         |

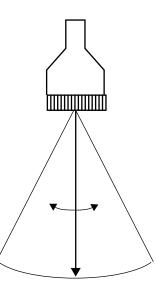

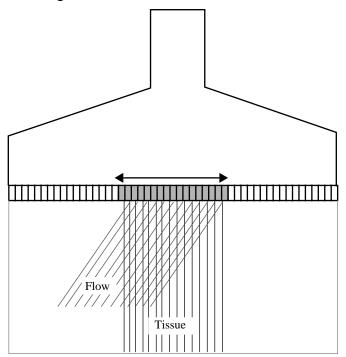

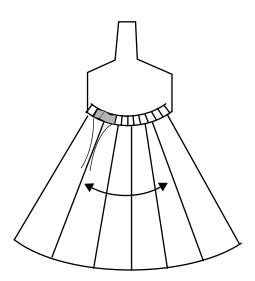

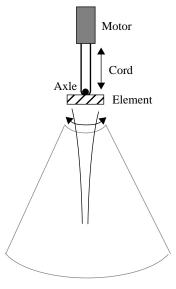

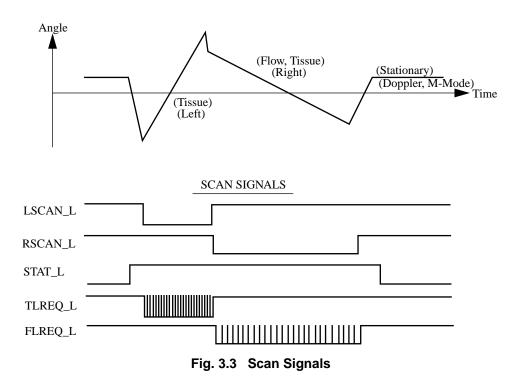

|                                        | 3.2               | Moving the Transducer Element                                 |         |

|                                        | 3.3               | The Ultrasound Beam                                           |         |

|                                        | 3.4               | Image Formats                                                 | . A1-23 |

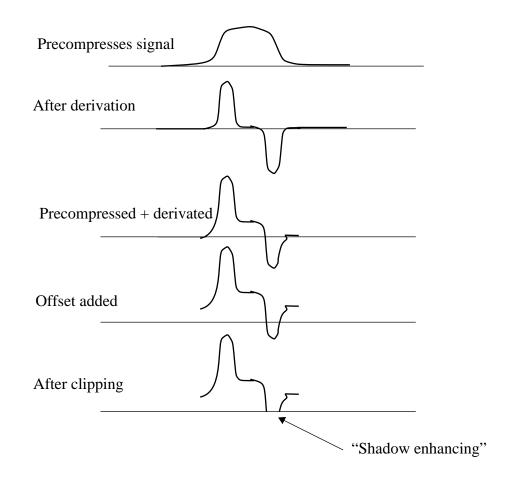

|                                        | <b>4.0</b><br>4.1 | Tissue Processing          General description                |         |

|                                        | 4.2               | Detailed descriptions of data processes                       | . A1-27 |

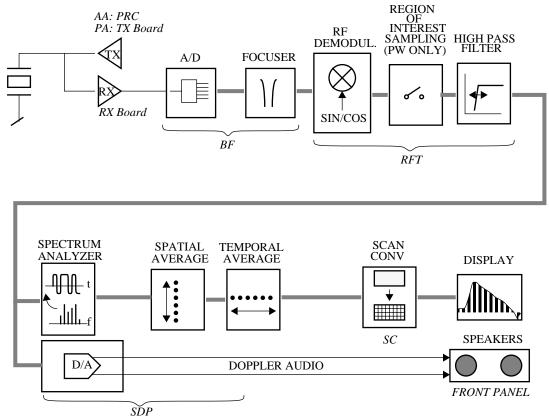

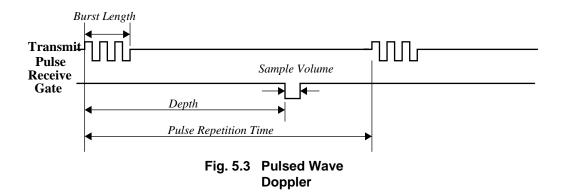

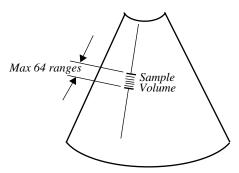

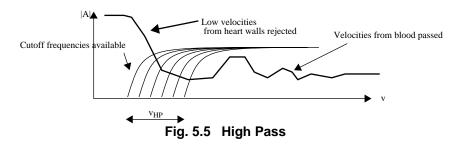

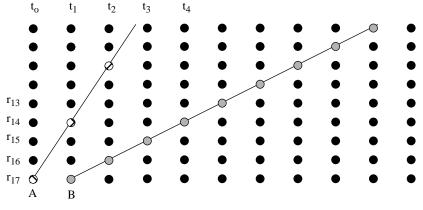

|                                        | <b>5.0</b><br>5.1 | Spectrum Doppler Processing                                   |         |

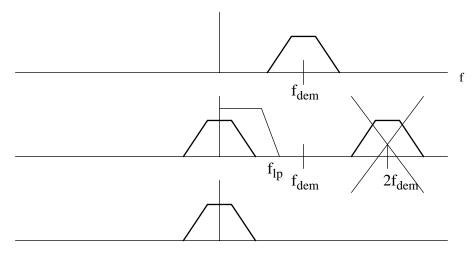

|                                        | 5.2               | Detailed descriptions of data processes                       |         |

|                                        | <b>6.0</b><br>6.1 | Color Flow Processing                                         |         |

Technical Skills Required ..... Intro-8

Repair ..... Intro-8

Test Equipment and Tools Required ..... Intro-9 General Tools..... Intro-9

Tools, Mobility Kit (Changing Wheels) ..... Intro-9

New Functions/ Features ..... Intro-12

Document History ..... Intro-12

Supported Features ..... Intro-12

#### SYSTEMFIVE System FiVe - Service Manual - FA091050 rev. I

| Chapter                                                            | Description                             | Page # |

|--------------------------------------------------------------------|-----------------------------------------|--------|

| 6.2                                                                | Detailed descriptions of data processes | A1-38  |

| 7.0                                                                | Post Processing                         | A1-42  |

| 7.1                                                                | Recursive Filtering                     |        |

| 7.2                                                                | Scan Conversion                         |        |

| 7.3                                                                |                                         |        |

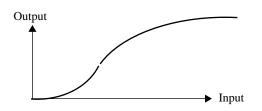

| 7.4                                                                | Compression and Reject                  |        |

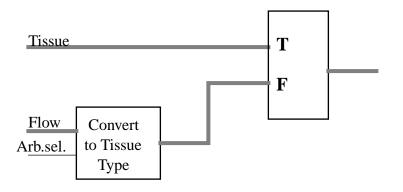

| 7.5                                                                | Arbitration                             | A1-44  |

| System Descrip-         8.0           tion - rev. 07         8.1   | Introduction                            |        |

| 8.2                                                                | Document History.                       |        |

| 9.0                                                                | General Information                     |        |

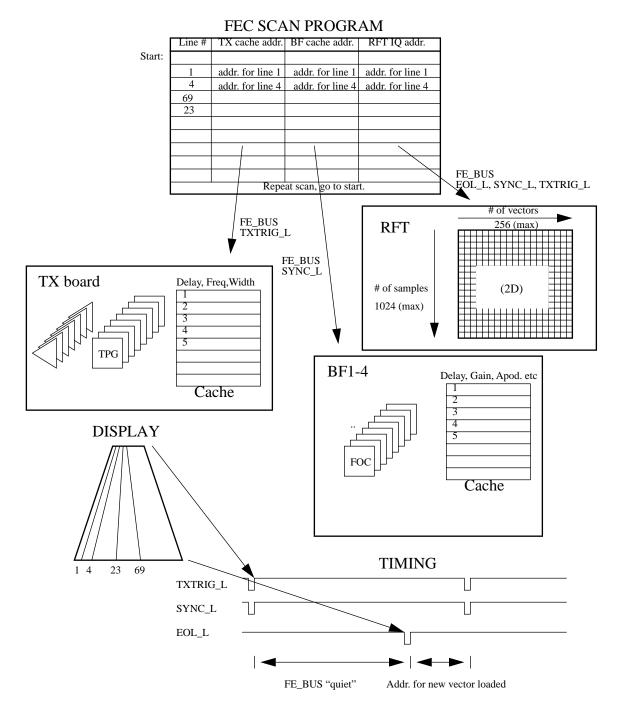

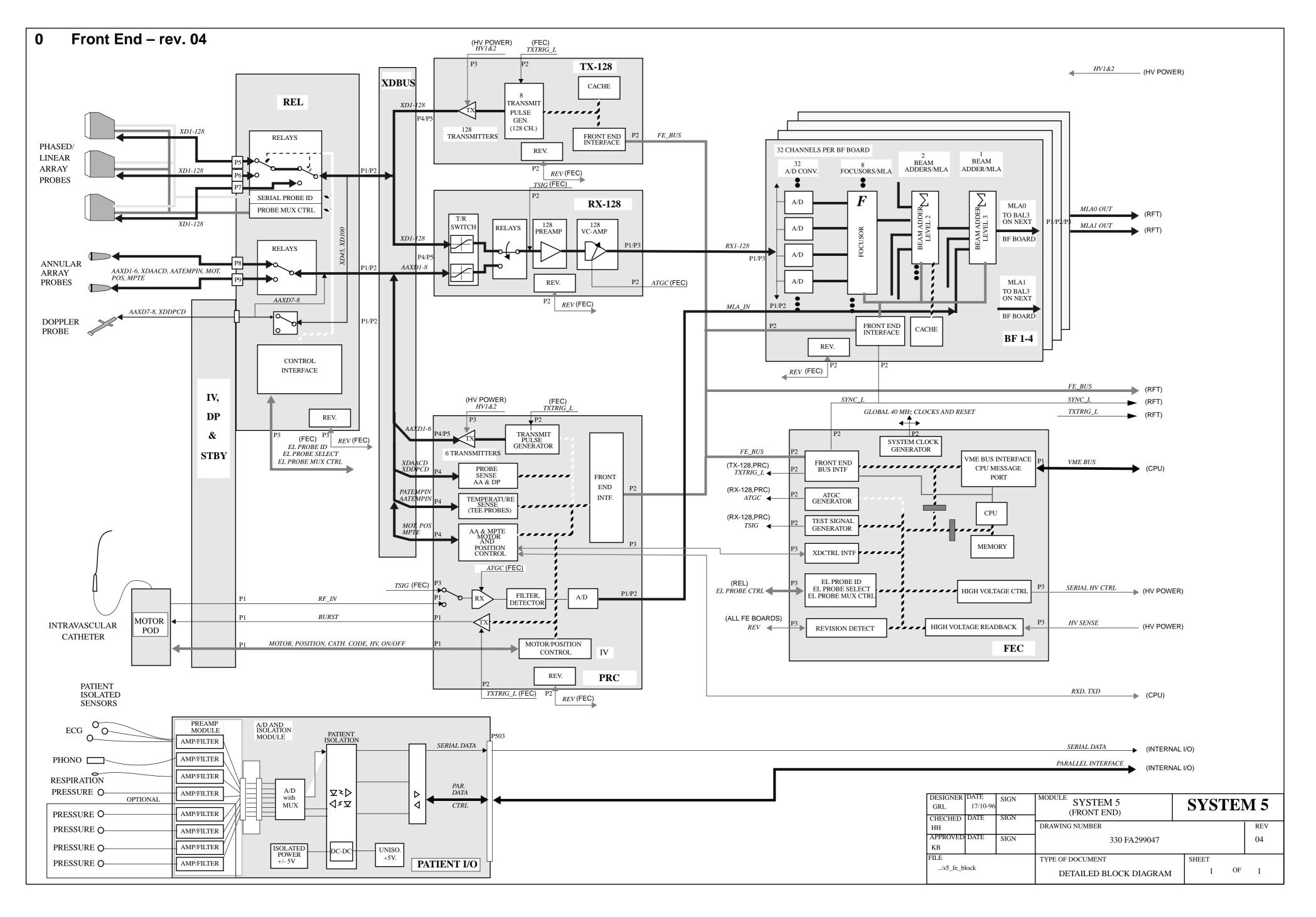

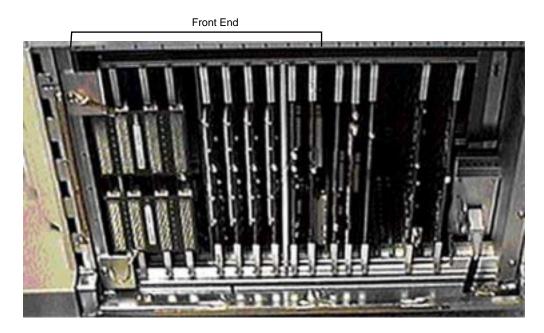

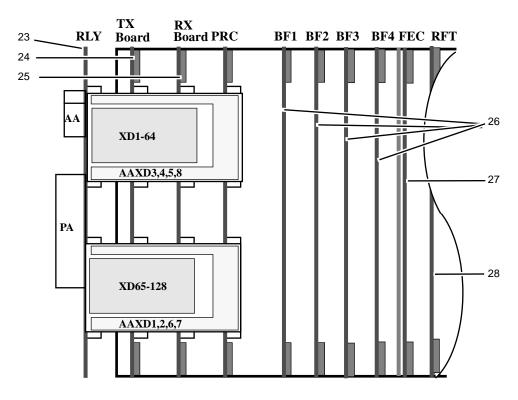

| 10.0                                                               | Front End                               |        |

| 10.1                                                               | General information                     |        |

| 10.2                                                               | Front End Bus                           | A1-46  |

| 10.3                                                               | Phased and Linear Array Front End.      | A1-46  |

| 10.4                                                               | Annular Array Front End                 | A1-48  |

| 10.5                                                               | Isolated inputs (incl. ECG and Phono)   | A1-48  |

| 10.6                                                               | High Voltage Power Supply               | A1-49  |

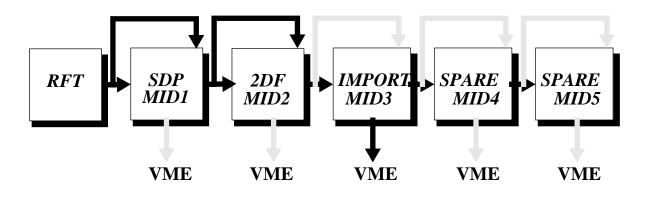

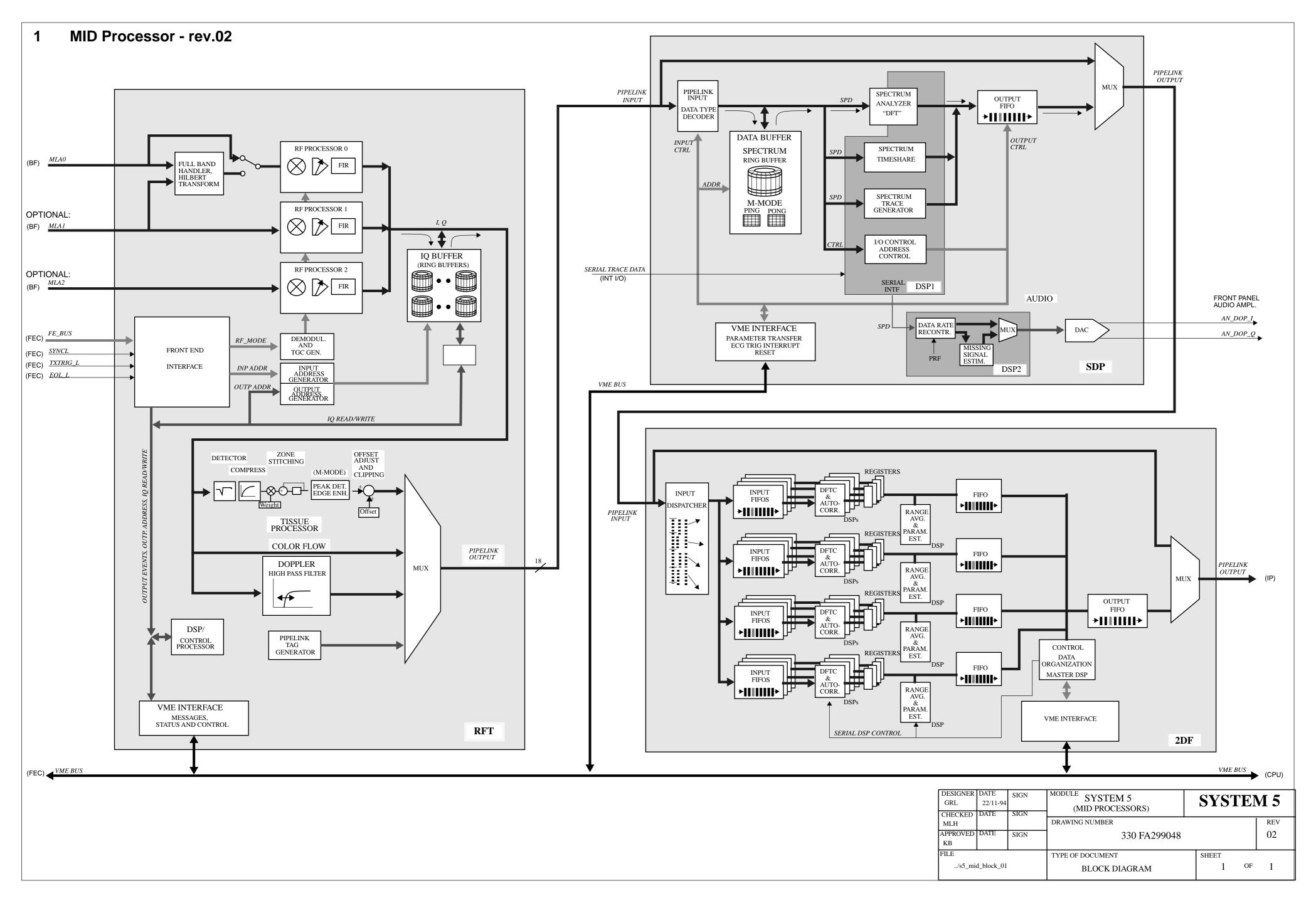

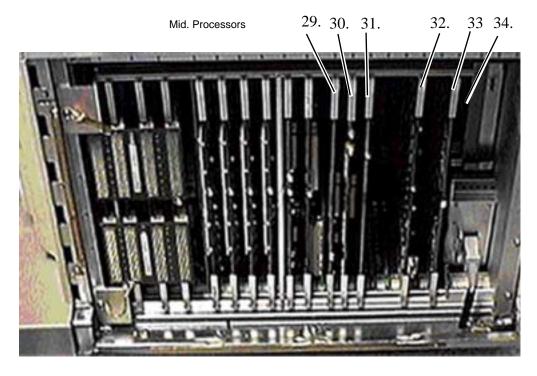

| 11.0                                                               | Mid Processors                          | A1-49  |

| 11.1                                                               | Pipelink bus                            | A1-49  |

| 11.2                                                               | RF and Tissue Processor (RFT)           | A1-49  |

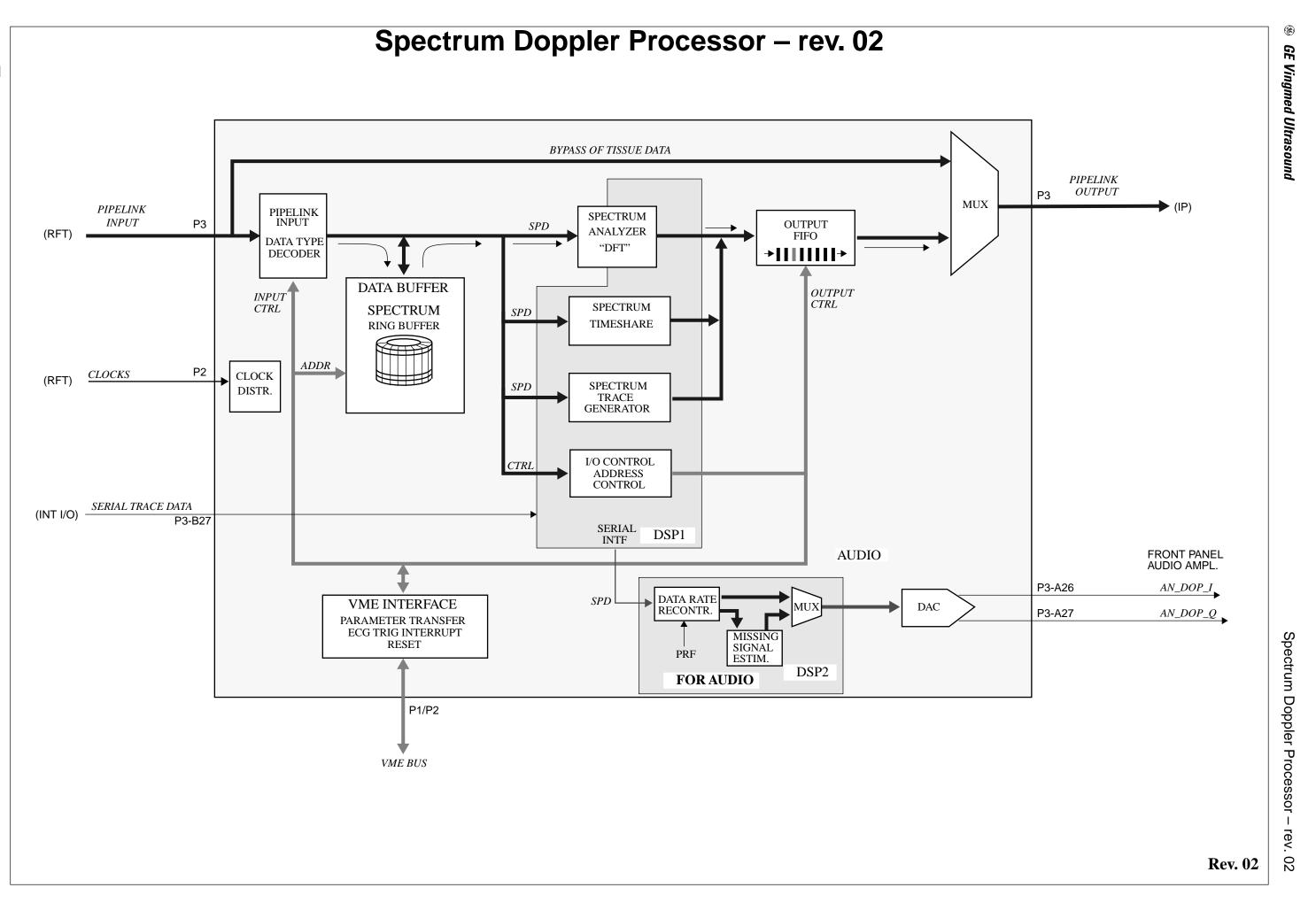

| 11.3                                                               | Spectrum Doppler Processor              | A1-50  |

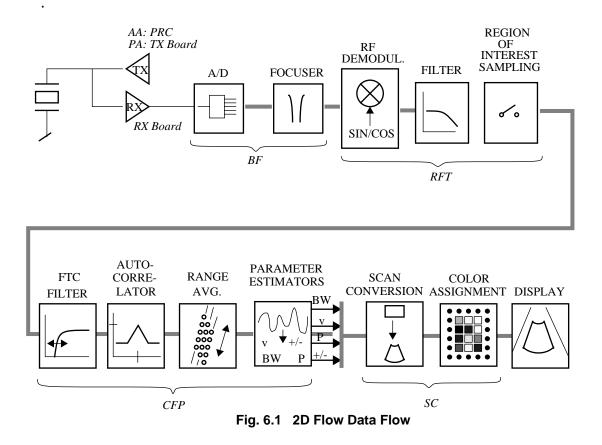

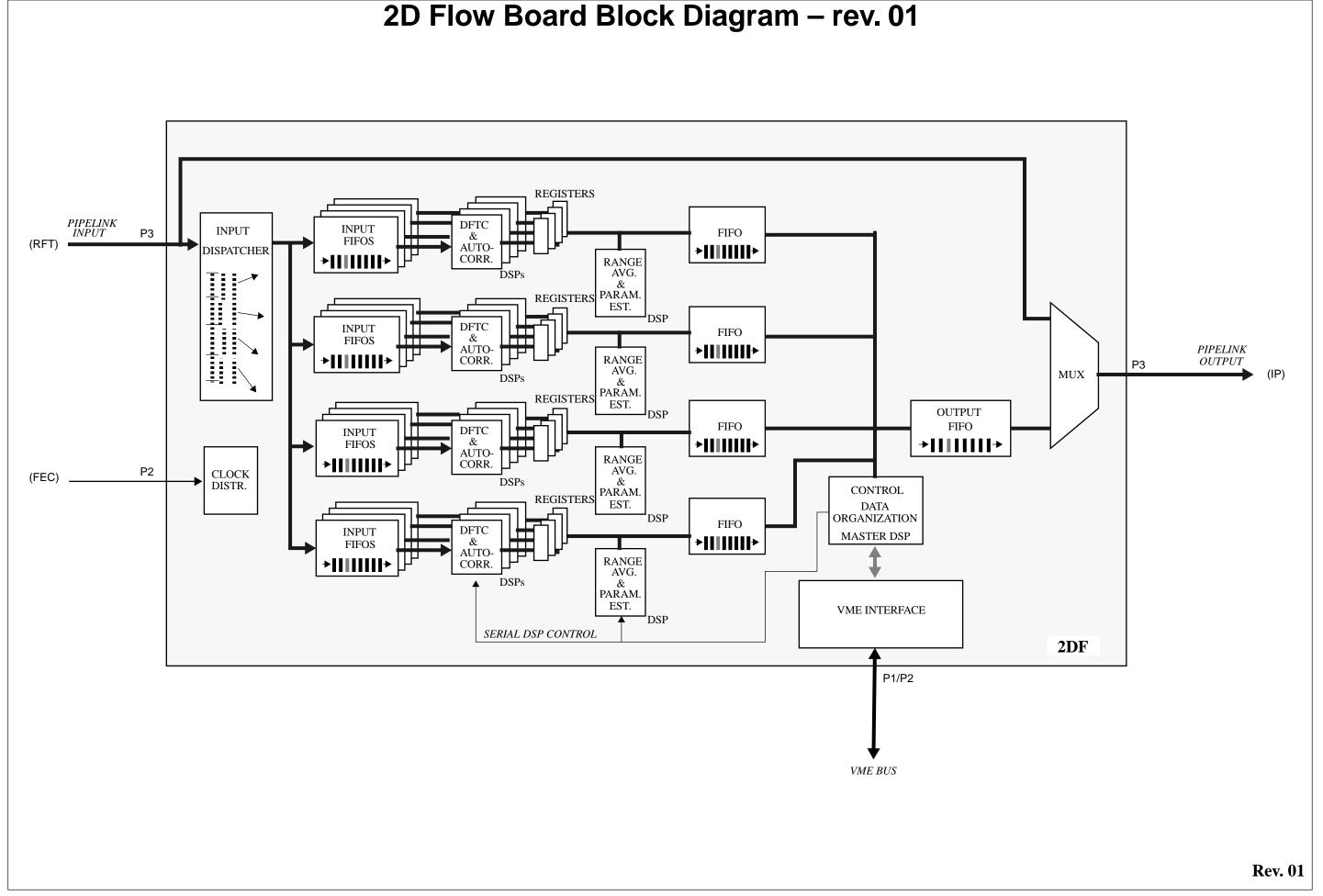

| 11.4                                                               | 2D Flow Processor                       | A1-51  |

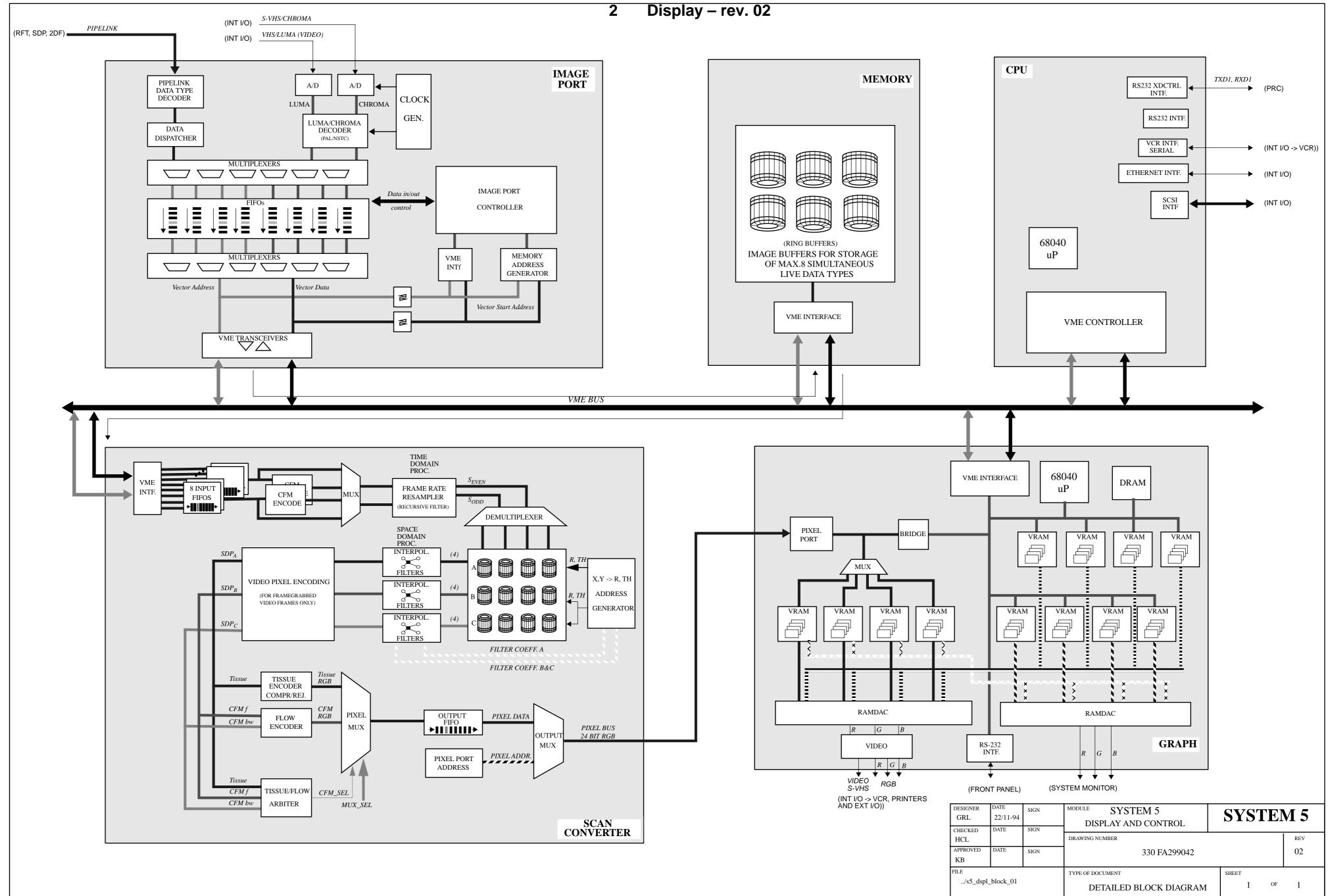

| 12.0                                                               | Display and Control                     |        |

| 12.1                                                               | Image Port                              |        |

| 12.2                                                               | Memory                                  |        |

| 12.3                                                               | Scan Converter                          |        |

| 12.4                                                               | Graphics Buffer                         |        |

| 12.5                                                               | System Control.                         |        |

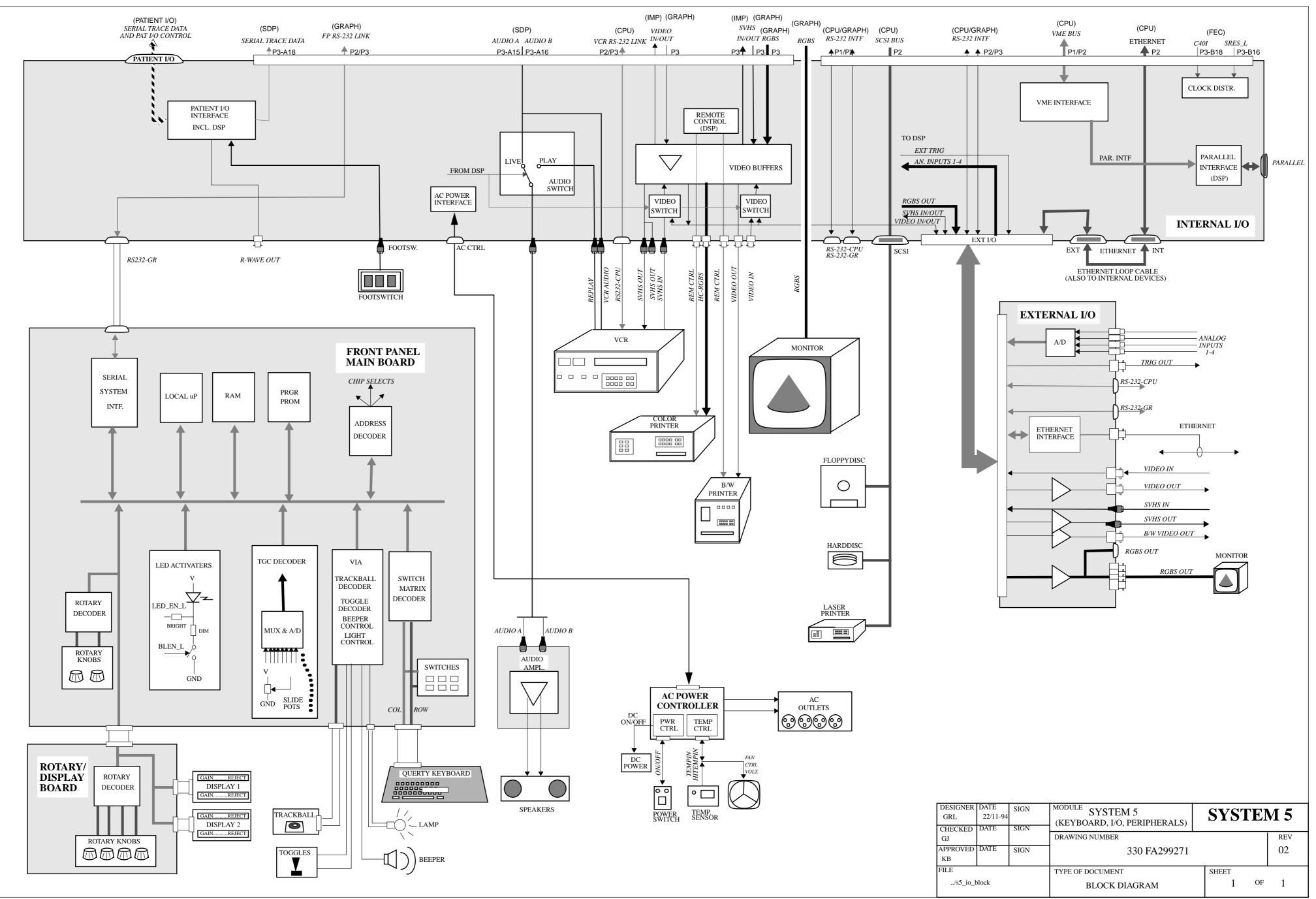

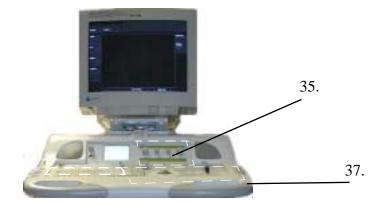

| <b>13.0</b><br>13.1                                                | Keyboard, I/O and Peripherals           | A1-55  |

| 13.2                                                               | External I/O to Rear Connector Panel    |        |

| 13.3                                                               | Keyboard                                | A1-56  |

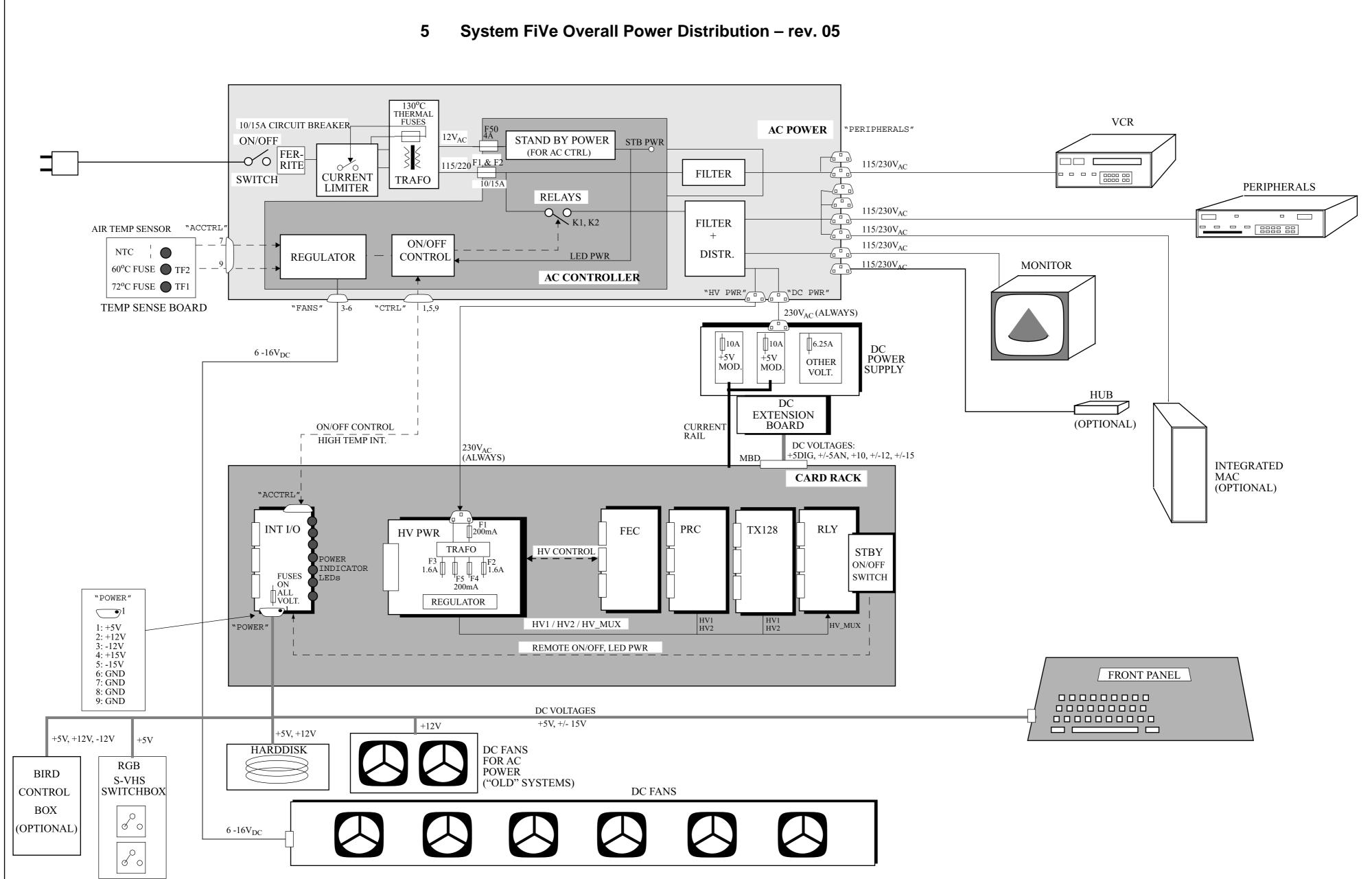

| Power Distribu-         14.0           tion - rev. 05         14.1 | Introduction                            | -      |

| 14.2                                                               | Document History.                       |        |

| 14.3                                                               | References                              |        |

| 15.0                                                               | Description                             |        |

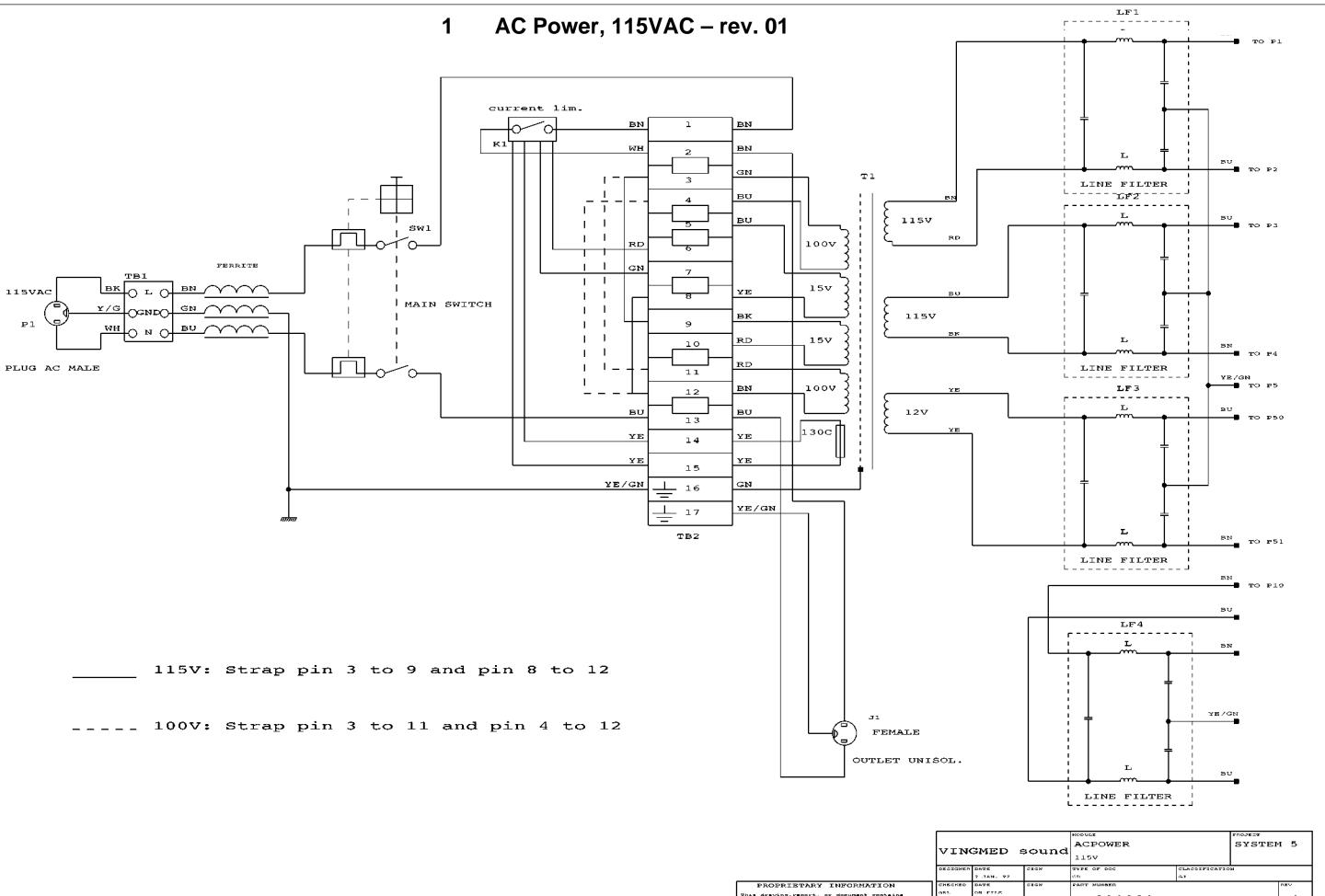

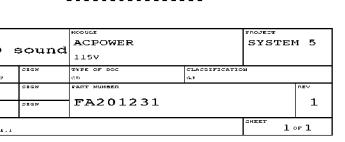

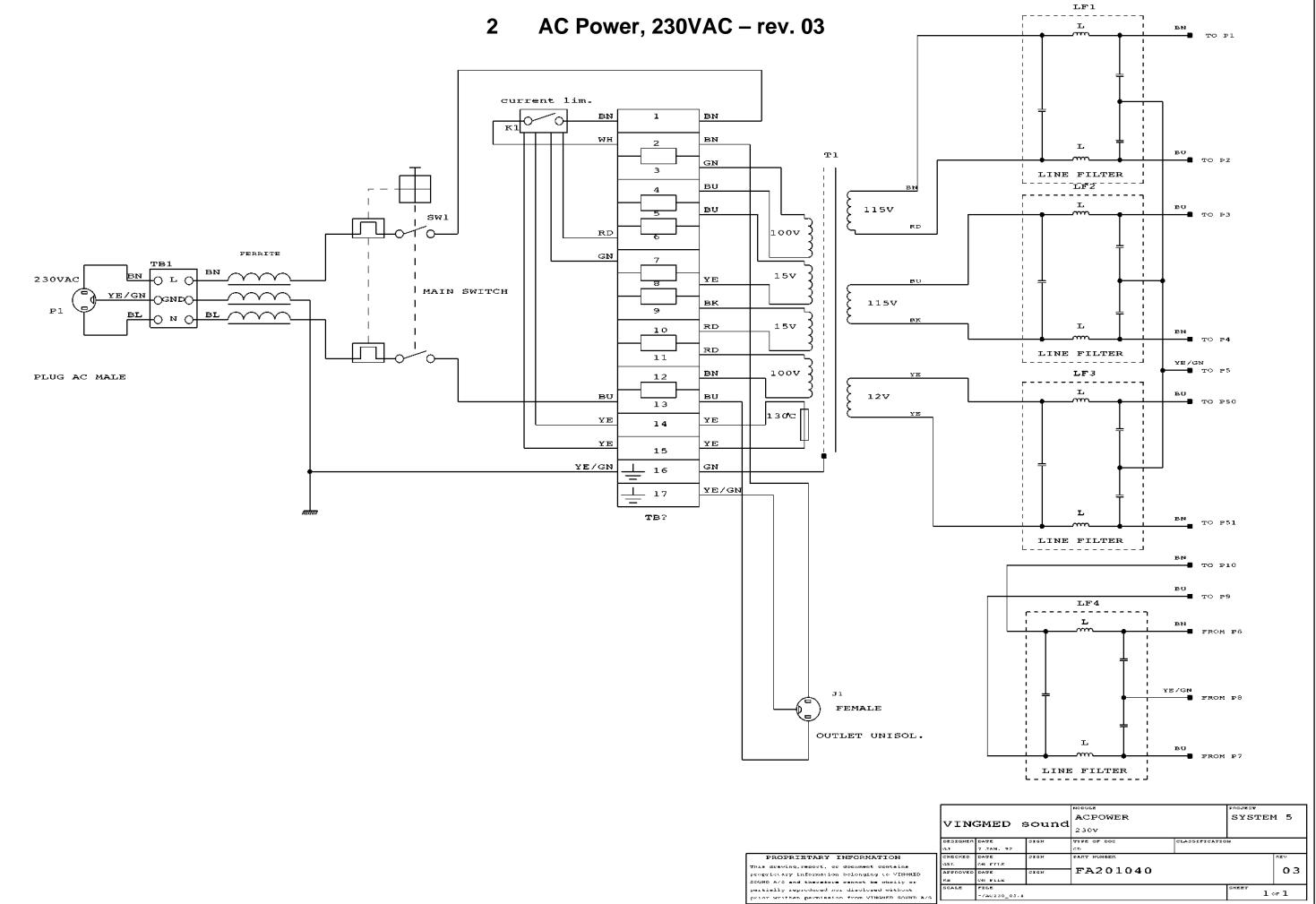

| 15.1                                                               | AC Power Supply.                        |        |

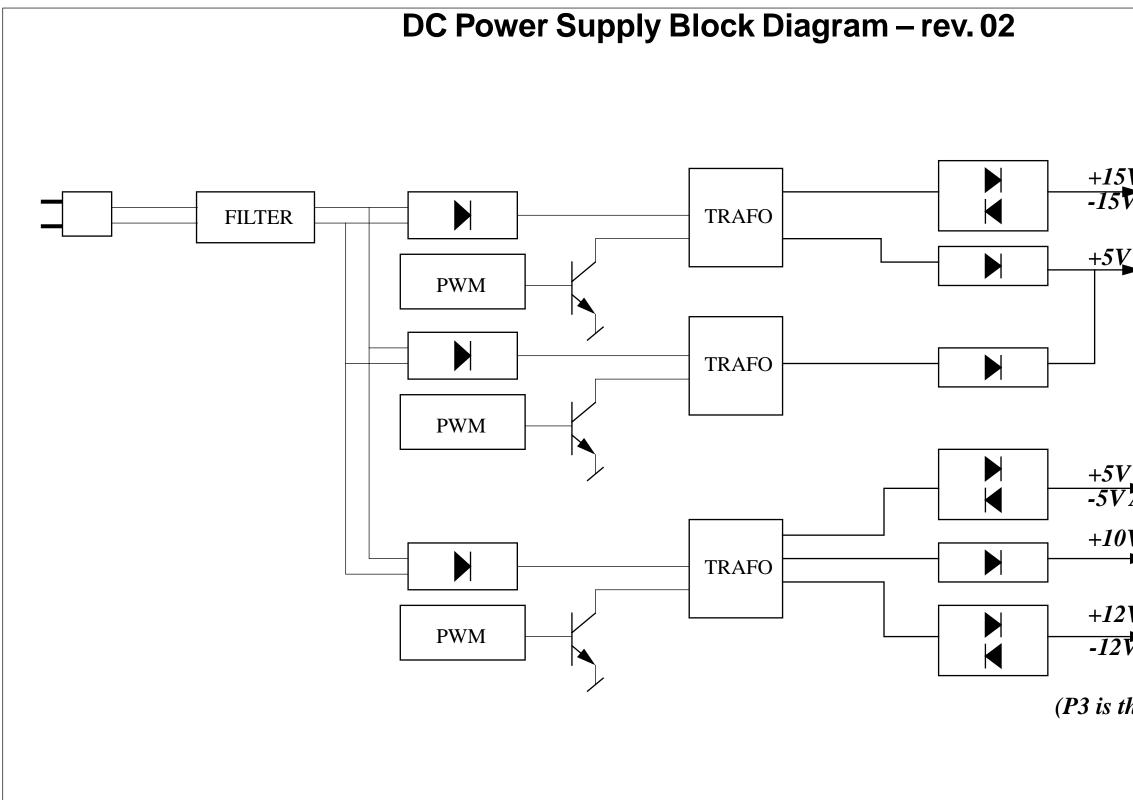

| 15.2                                                               | DC Power Supply                         |        |

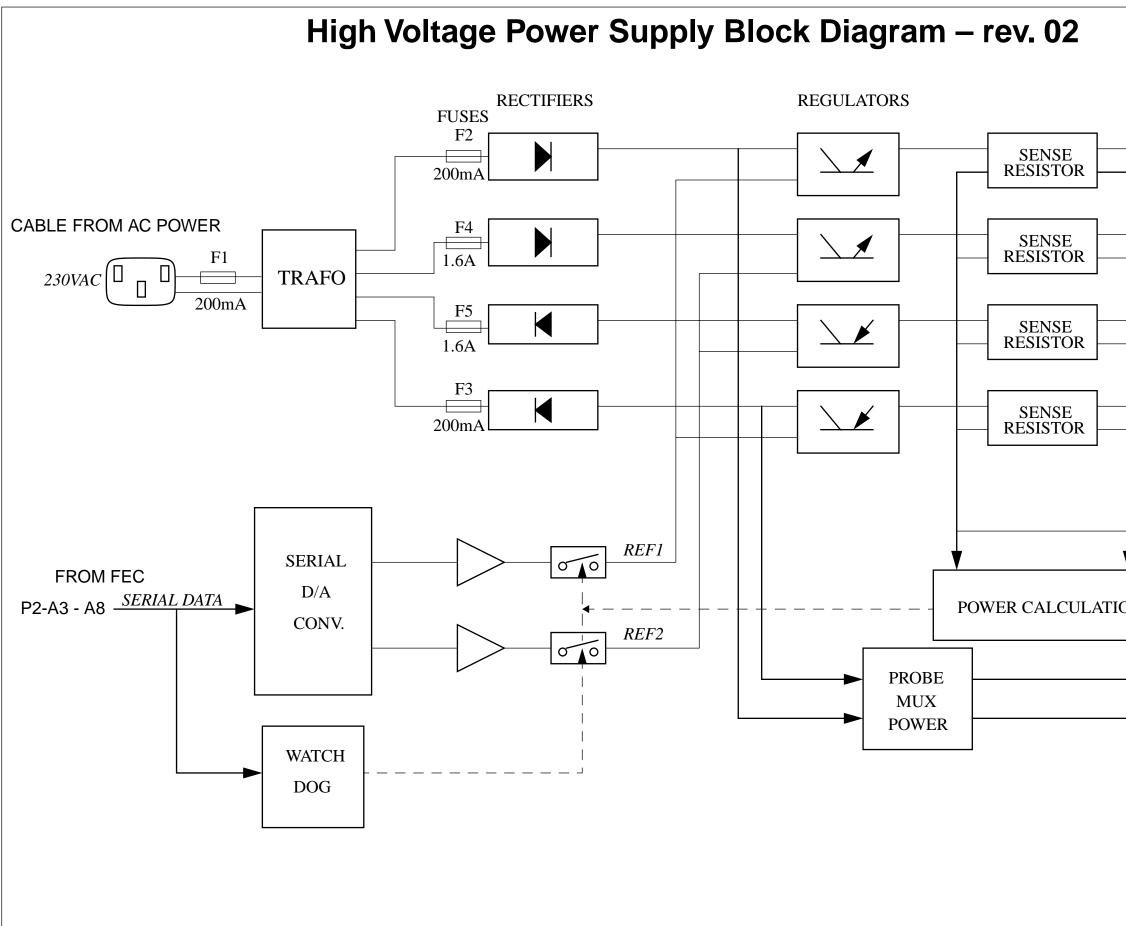

| 15.3                                                               | High Voltage Power Supply               |        |

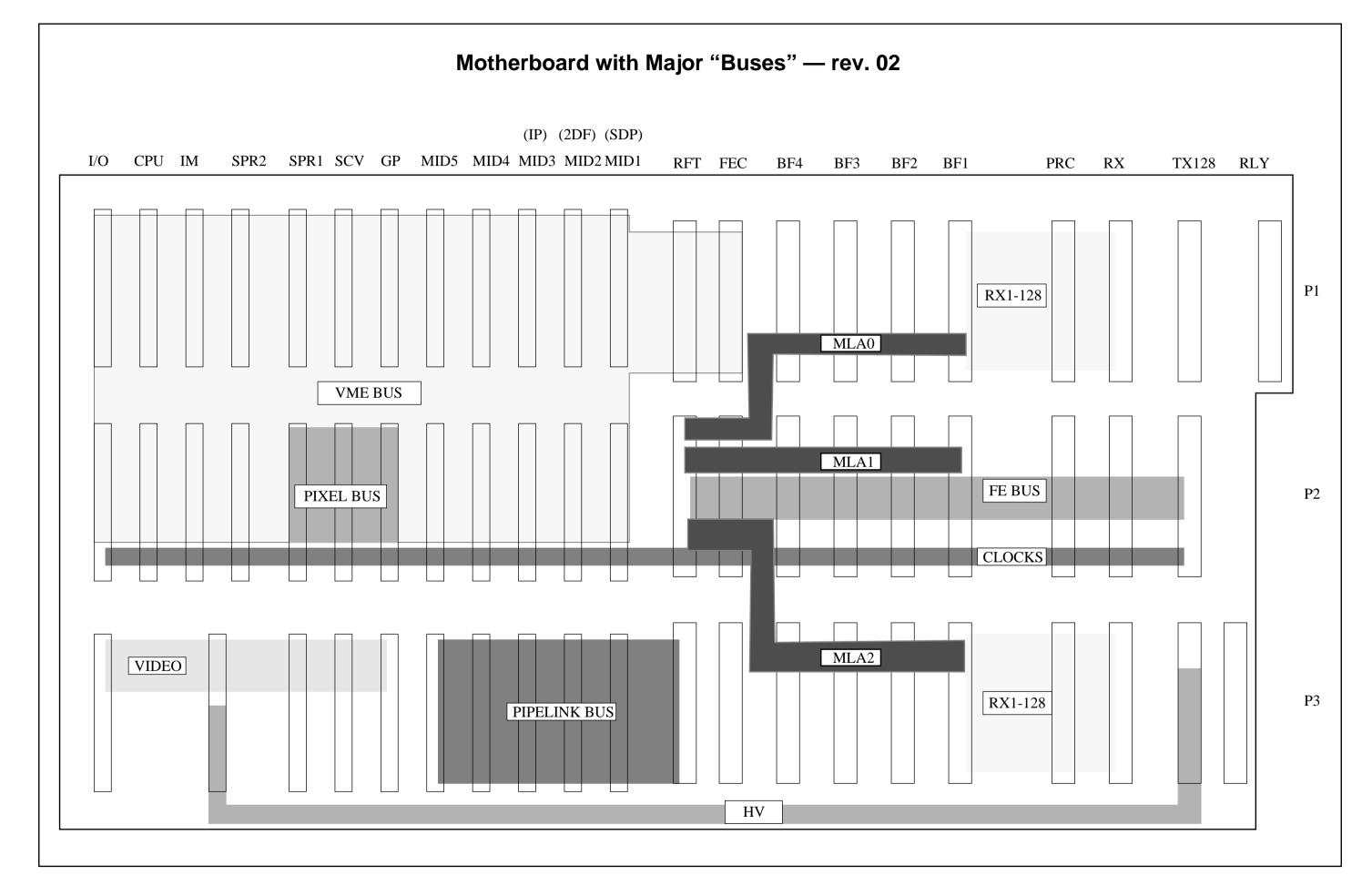

| Bus Distribution – 16.0                                            | Introduction                            |        |

| rev. 05 16.1<br>16.2                                               | Abstract                                |        |

| 16.2                                                               | Document History                        |        |

|                                                                    |                                         |        |

| <b>17.0</b><br>17.1                                                | Front End Bus                           |        |

| 17.2                                                               | Slaves:                                 |        |

| 17.3                                                               | Description                             |        |

|                                 | Chapt                                                                                                                                                                  | er Description                                                                                                                                                                                                                                                                                                                               | Page #                                                                               |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

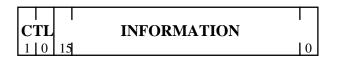

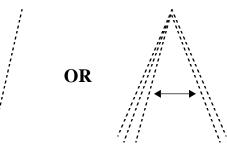

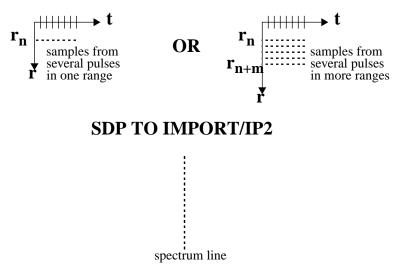

|                                 | <b>18.0</b><br><b>19.0</b><br>19.1<br>19.2<br>19.3<br><b>20.0</b><br>20.1<br>20.2<br><b>21.0</b>                                                                       | MLA Buses         Pipelink Bus         Pipelink Bus Format:         Pipelink Control (CTL):         Pipelink Dataflow:         VME Bus (VME 64)         Control/Setup         Data Flow         Pixel Bus                                                                                                                                    | A1-62<br>A1-62<br>A1-63<br>A1-63<br>A1-63<br>A1-65<br>A1-65<br>A1-66                 |

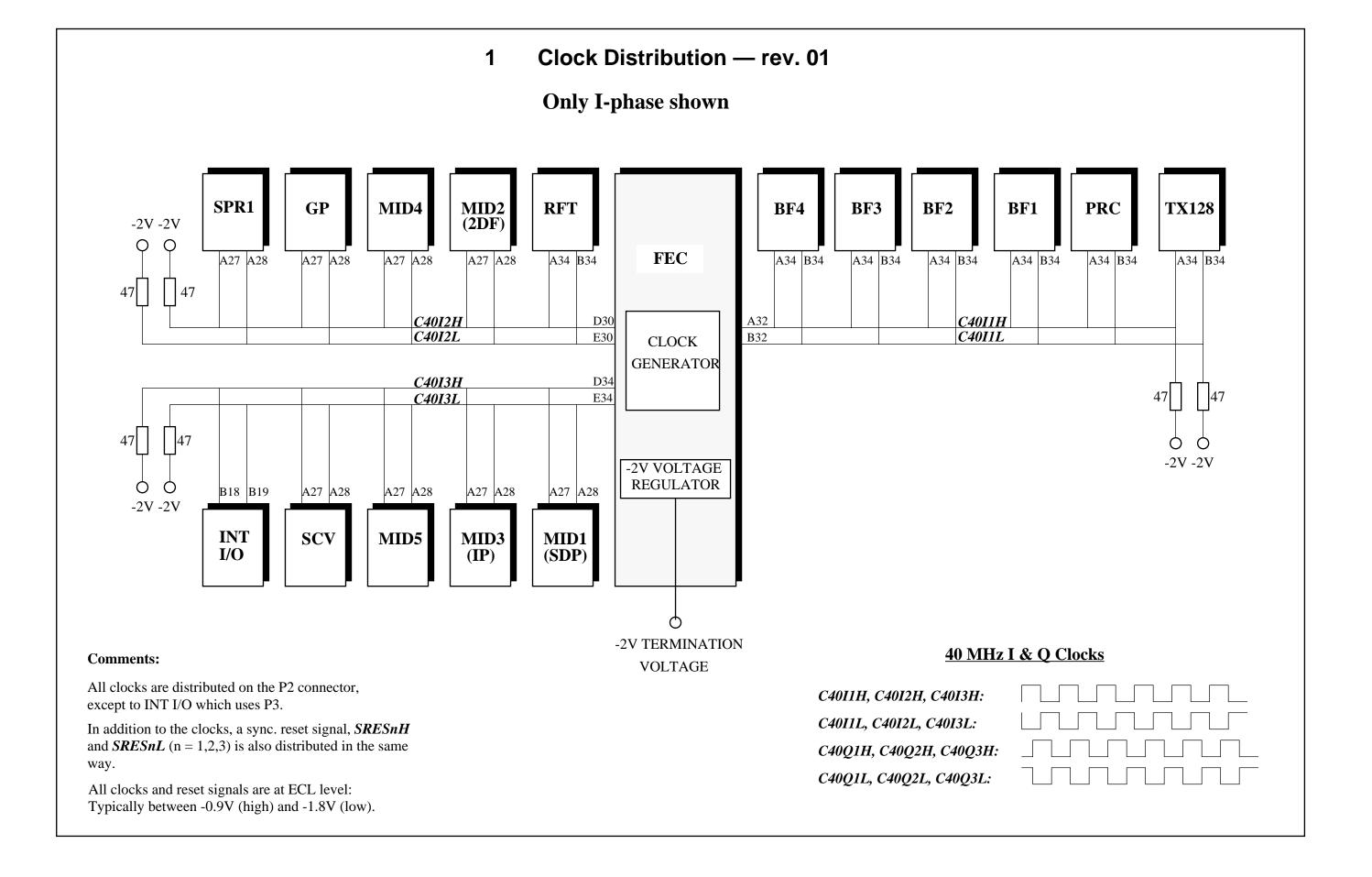

| Clock Distribution<br>– rev. 04 | <b>22.0</b><br>22.1<br>22.2<br>22.3<br><b>23.0</b>                                                                                                                     | Introduction<br>Abstract<br>Document History<br>References<br>Description                                                                                                                                                                                                                                                                    | A1-68<br>A1-68<br>A1-68                                                              |

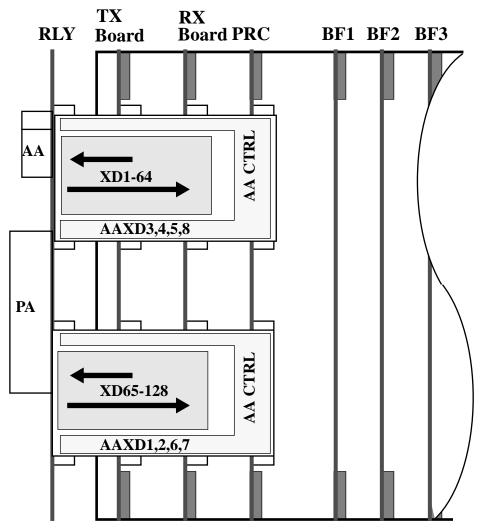

| Board Formats –<br>rev. 02      | 24.0<br>24.1<br>24.2<br>25.0<br>26.0<br>27.0<br>28.0<br>29.0<br>30.0<br>31.0                                                                                           | Introduction<br>Abstract<br>Document History<br>RLY<br>TX128, RX128, RX64 and PRC<br>BF1-4, FEC and RFT<br>SDP, 2DF, IMPORT, IP2, SCONV and GRAPHIC<br>CPU and IMMEM<br>INT I/O<br>HV POWER                                                                                                                                                  | A1-69<br>A1-69<br>A1-70<br>A1-71<br>A1-72<br>A1-73<br>A1-74<br>A1-75                 |

| The Front End Mo                | odules                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                              |                                                                                      |

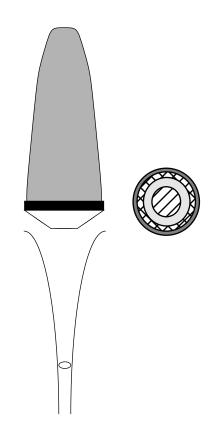

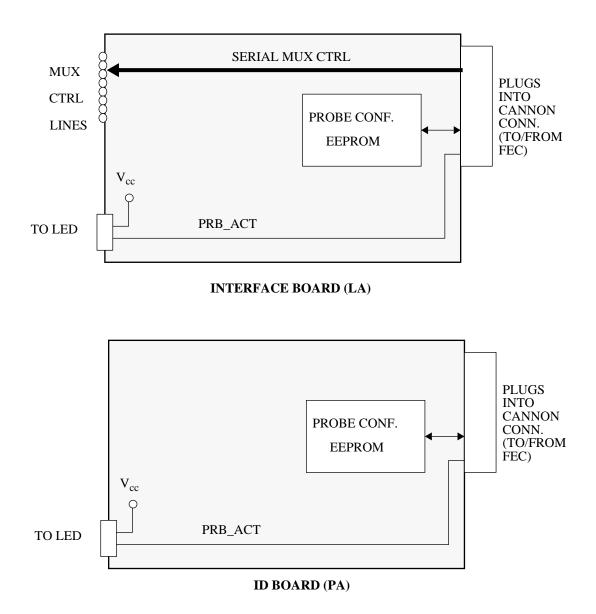

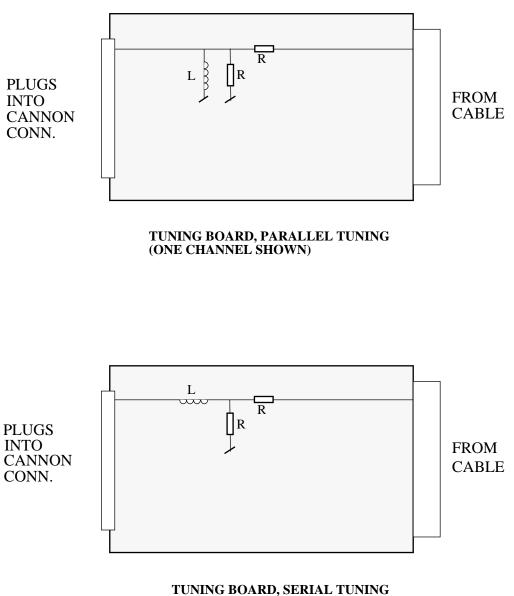

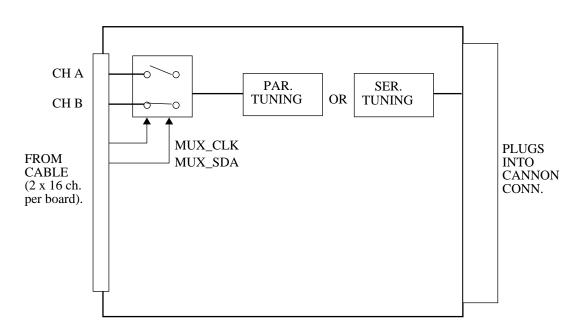

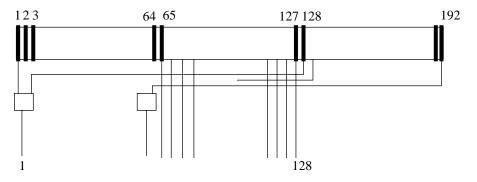

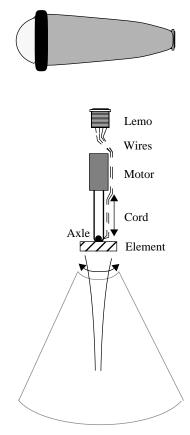

| Probe Description<br>- rev. 06  | <ol> <li>1.0</li> <li>1.1</li> <li>1.2</li> <li>1.3</li> <li>1.4</li> <li>2.0</li> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>3.0</li> <li>3.1</li> <li>3.2</li> </ol> | Introduction         Abstract         Document History         Abbreviations/Nomenclature/Definitions         References         Electronically Steered Probes         Overview         Connector Interfaces         Module Descriptions         Mechanically Steered Probes         Trans-thorax Probes         Transesophageal probes (TE) | A2-3<br>A2-3<br>A2-3<br>A2-3<br>A2-3<br>A2-3<br>A2-4<br>A2-5<br>A2-9<br>A2-9<br>A2-9 |

| Probe Cable                     | <b>4.0</b><br>4.1<br>4.2<br>4.3<br>4.4<br><b>5.0</b>                                                                                                                   | Introduction         Abstract         Document History         Definitions/Abbreviations/Nomenclature         References         Descriptions                                                                                                                                                                                                | A2-11<br>A2-11<br>A2-11<br>A2-11<br>A2-11                                            |

| IV & DP Connector<br>Board      | <b>6.0</b><br>6.1                                                                                                                                                      | Introduction                                                                                                                                                                                                                                                                                                                                 |                                                                                      |

6.2

6.3

Document History ..... A2-12

Definitions/Abbreviations/Nomenclature ..... A2-12

|                   | Chapter             | Description                                 | Page # |

|-------------------|---------------------|---------------------------------------------|--------|

|                   | 7.0                 | Physical Dimensions                         | A2-12  |

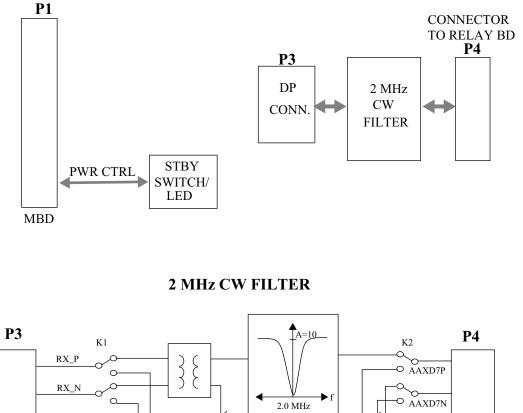

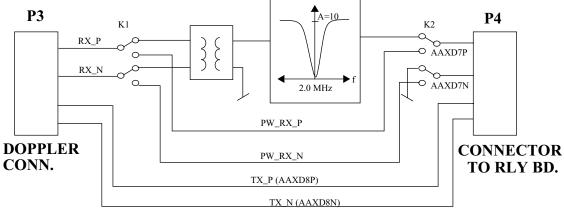

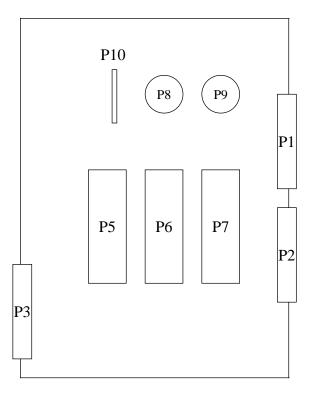

|                   | 8.0                 | General Description and Block Diagram       |        |

|                   | 8.1                 | Block Diagrams                              |        |

|                   | 8.2                 | Standby Power Switch                        |        |

|                   | 8.3                 | 2 MHz CW Filter                             |        |

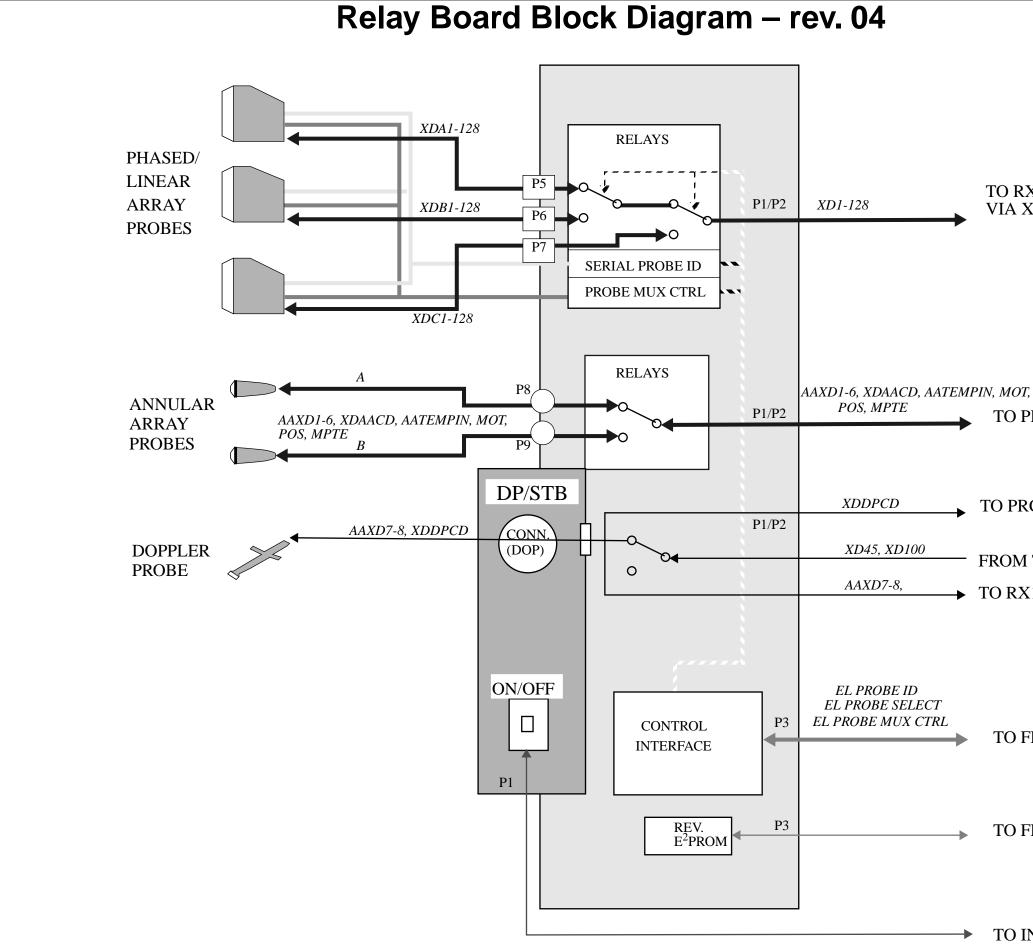

| Relay Board - RLY | 9.0                 | Introduction                                |        |

| rev. 03           | 9.1                 | Abstract                                    | -      |

|                   | 9.2                 | Document History.                           |        |

|                   | 9.3                 | Definitions/Abbreviations/Nomenclature      |        |

|                   | 9.4                 | References                                  |        |

|                   | 10.0                | Physical Dimensions                         |        |

|                   | <b>11.0</b><br>11.1 | Connectors and descriptions                 |        |

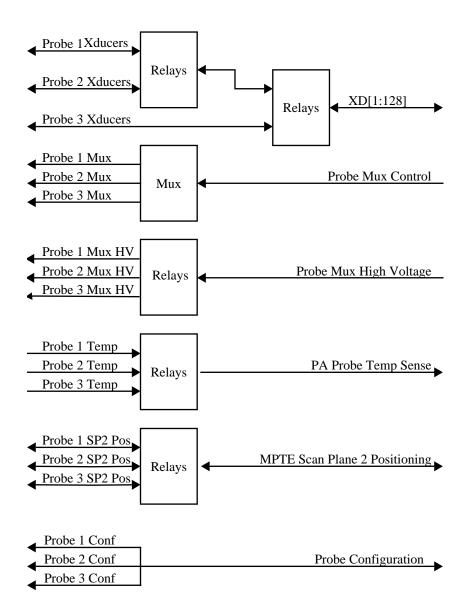

|                   | 11.2                | Phased- and Linear Array Connectors         |        |

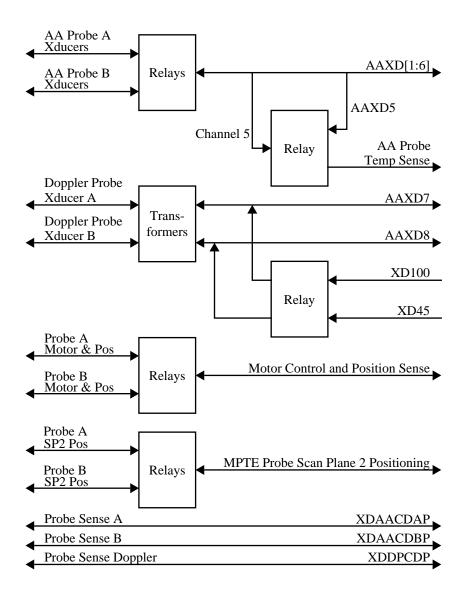

|                   | 11.3                | Annular Array and Doppler Probe Connections |        |

|                   | 11.4                | Control Interface.                          |        |

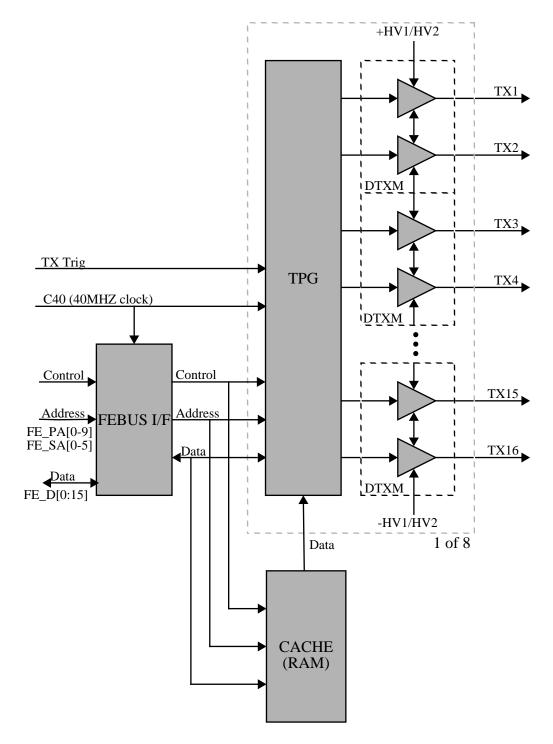

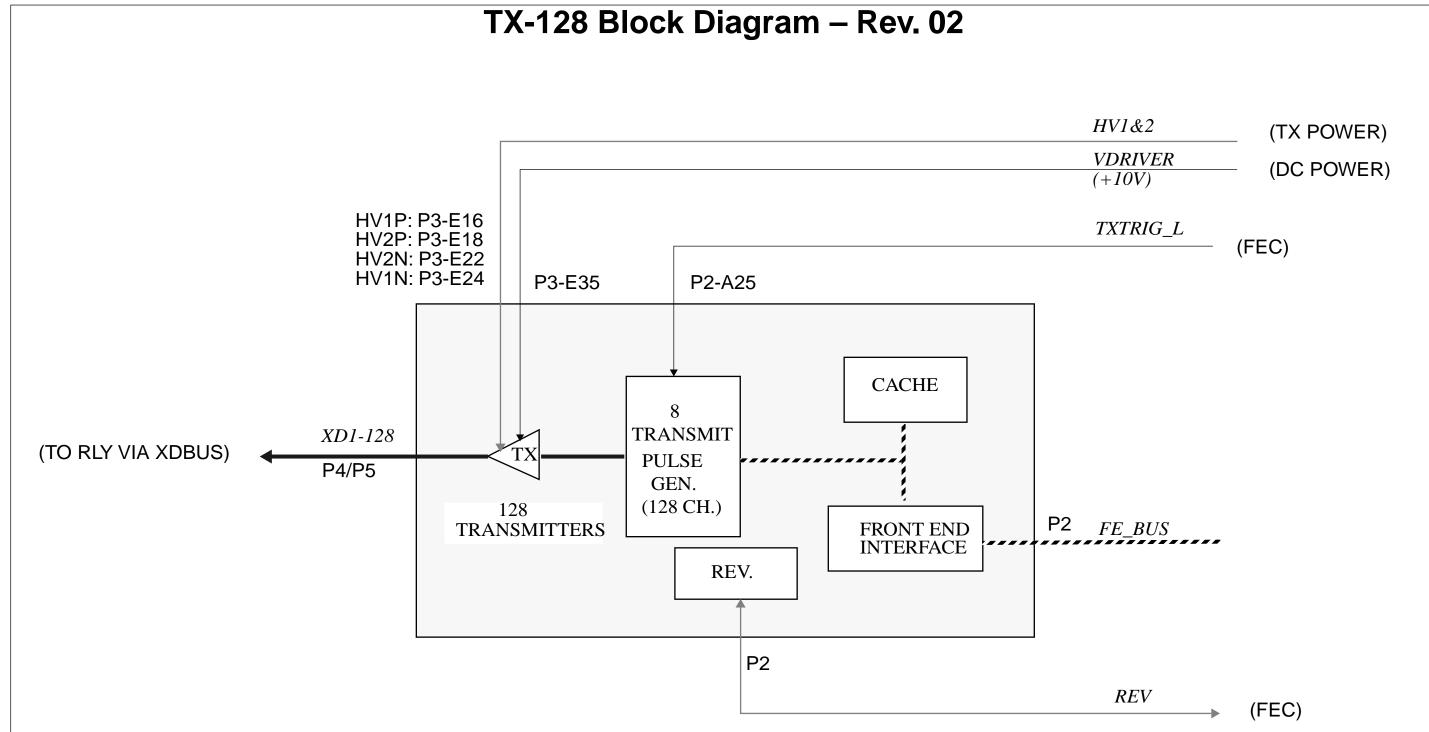

| Transmitter Board | 12.0                | Overview                                    | A2-20  |

| - TX128 – rev. 04 | 12.1                | Abstract                                    | A2-20  |

|                   | 12.2                | Document History                            | A2-20  |

|                   | 12.3                | Definitions/Abbreviations/Nomenclature      | A2-20  |

|                   | 12.4                | References                                  | A2-20  |

|                   | 13.0                | Inputs                                      | A2-20  |

|                   | 14.0                | General Description                         |        |

|                   | 14.1                | Overview                                    |        |

|                   | 14.2                | Dual Transmitter Module                     |        |

|                   | 14.3                | Transmit Pulse Generator ASIC.              |        |

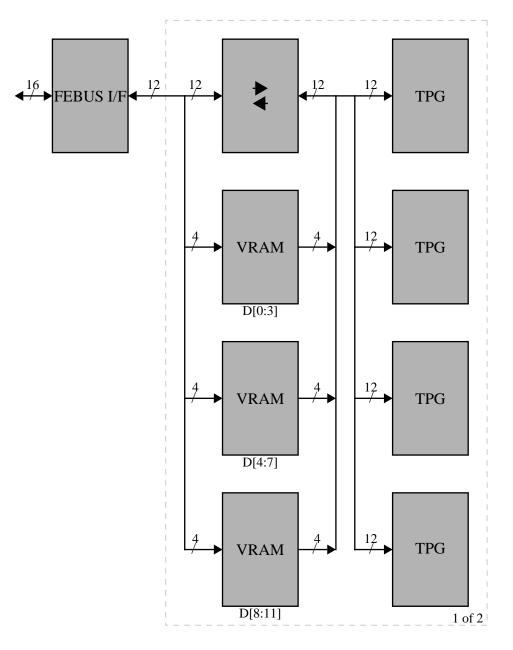

|                   | 14.4                | RAM Cache (VRAM)                            |        |

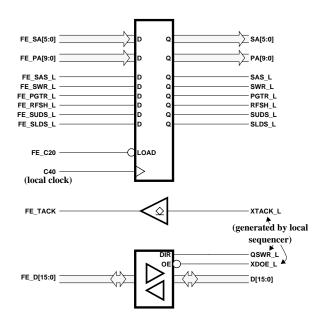

|                   | 14.5                | FE Bus Interface                            |        |

|                   | 15.0                | Outputs                                     |        |

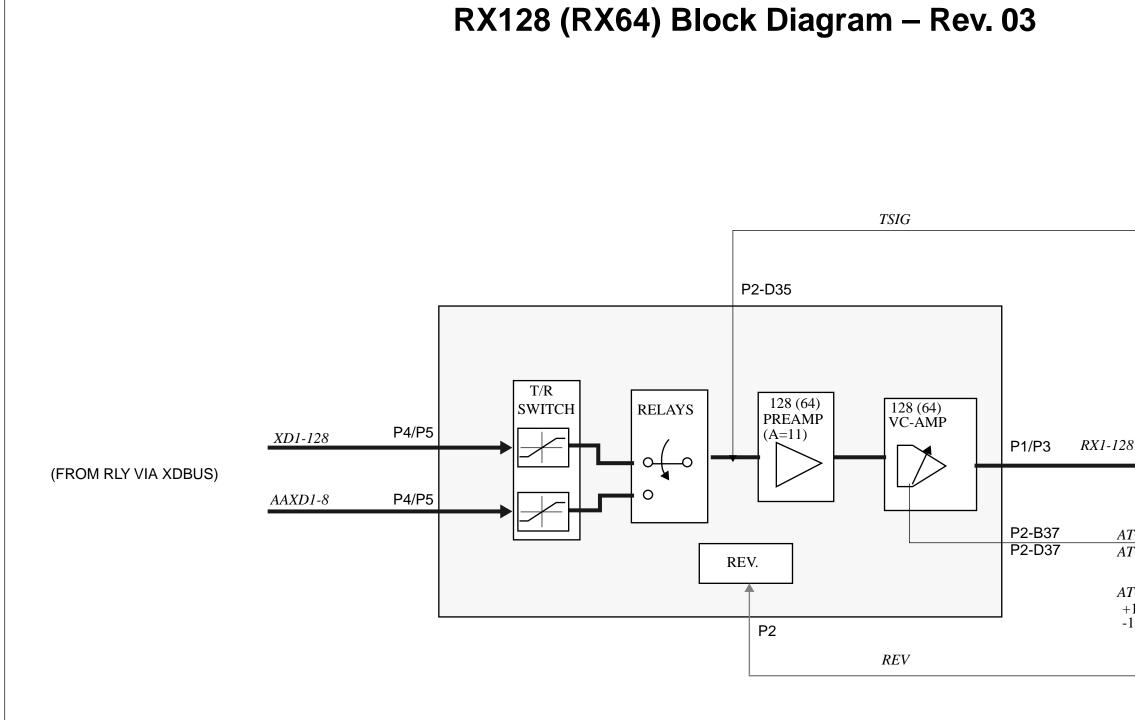

| Receiver Board -  | 16.0                | Introduction                                |        |

| RX 128 - rev.02   | 16.1                | Abstract                                    |        |

|                   | 16.2                | Document History.                           |        |

|                   | 16.3                | Definitions/Abbreviations/Nomenclature      |        |

|                   | 17.0                | Inputs                                      |        |

|                   | <b>18.0</b><br>18.1 | General Description                         |        |

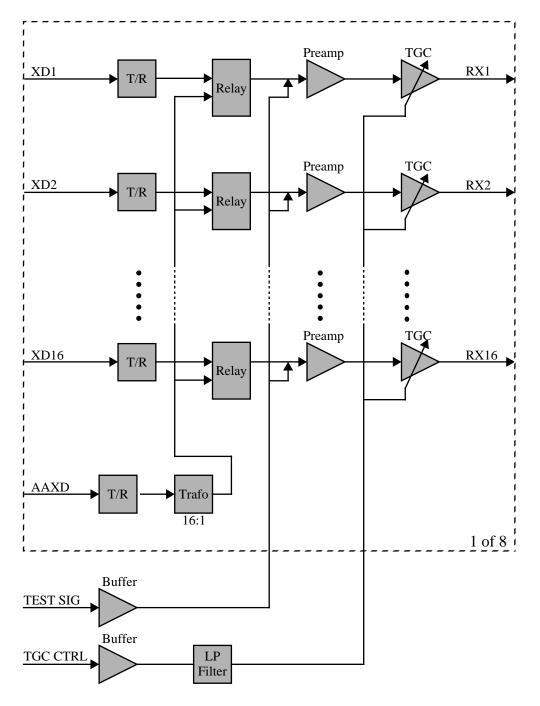

|                   | 18.2                | T/R Switches                                |        |

|                   | 18.3                | Preamplifiers                               |        |

|                   | 18.4                | TGC Amplifiers                              |        |

|                   | 18.5                | Annular Array Channels                      |        |

|                   | 18.6                | Control and Test Signal Interface.          |        |

|                   | 19.0                | Outputs                                     |        |

| Receiver Board -  | 20.0                |                                             | A2-29  |

| RX 64 rev.02      | 20.1                | Abstract                                    | -      |

|                   | 20.2                | Document History                            |        |

|                   | 20.3                | Definitions/Abbreviations/Nomenclature      |        |

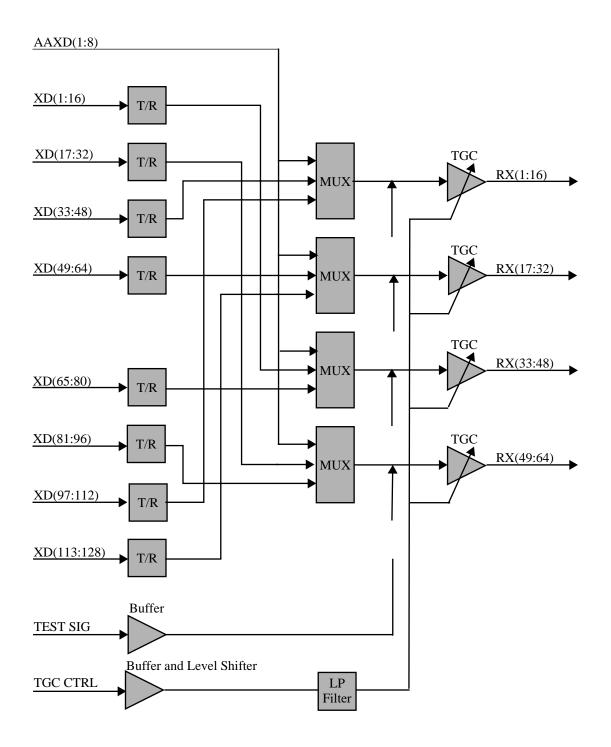

|                   | 21.0                | General Description                         |        |

|                   | 21.1                | Overview                                    |        |

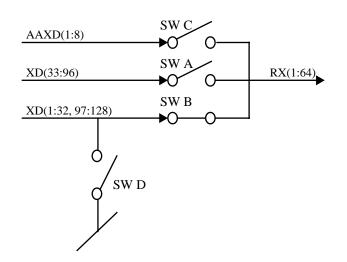

|                   | 21.2                | T/R Switches                                | A2-31  |

|                     | Chapte              | r Description                                                               | Page # |

|---------------------|---------------------|-----------------------------------------------------------------------------|--------|

|                     | 21.3<br>21.4        | Input Multiplexers                                                          | A2-32  |

|                     | 21.5<br>21.6        | TGC Control and Test Signal Interface         Multiplexer Control Interface |        |

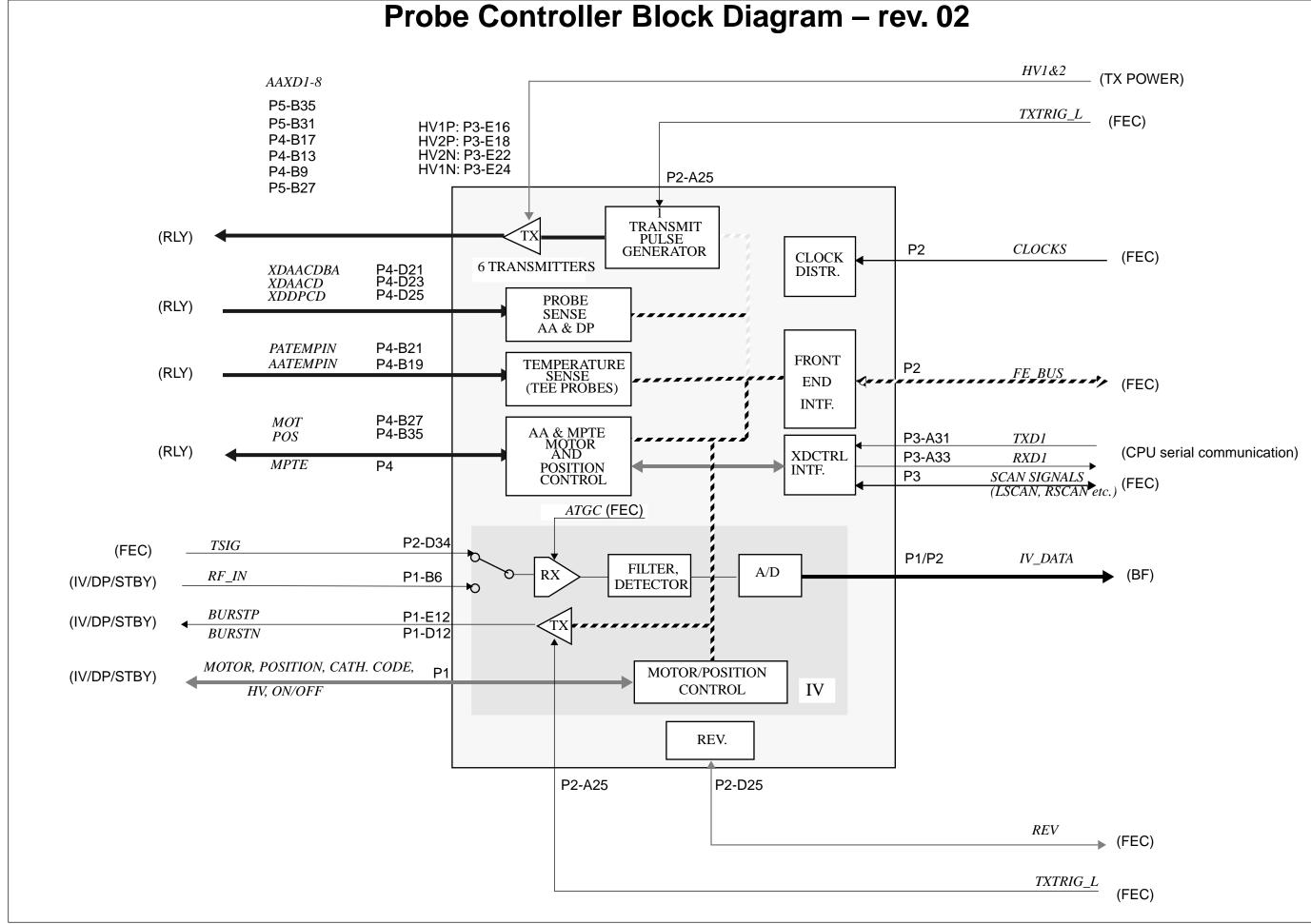

| Probe Controller    | <b>22.0</b>         | Overview.                                                                   |        |

| Board - PRC – rev.  | 22.1                | Abstract                                                                    |        |

| 04                  | 22.2                | Document History                                                            |        |

|                     | 22.3<br>22.4        | References                                                                  |        |

|                     | 22.4<br>23.0        | Inputs                                                                      |        |

|                     | 23.0                | Descriptions                                                                |        |

|                     | 24.0                | Annular Array and Doppler Transmitter                                       |        |

|                     | 24.2                | Annular Array and Stand Alone Doppler Probe Sense                           |        |

|                     | 24.3                | Temperature Sensors                                                         |        |

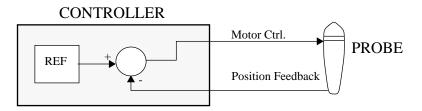

|                     | 24.4                | Annular Array Probe Motor Control                                           |        |

|                     | 24.5                | Front End Bus Interface                                                     |        |

|                     | 24.6                | Clock Distribution.                                                         |        |

|                     | 25.0                | Control                                                                     |        |

|                     | 26.0                | Outputs                                                                     |        |

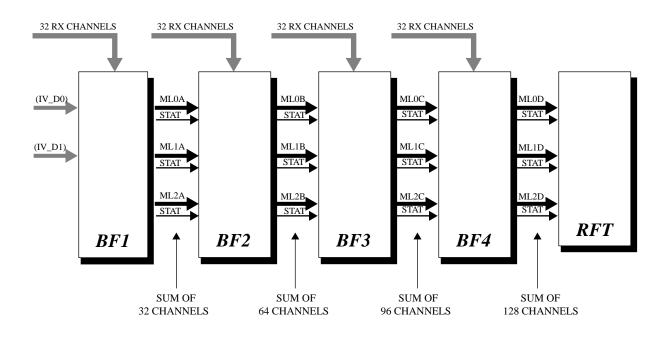

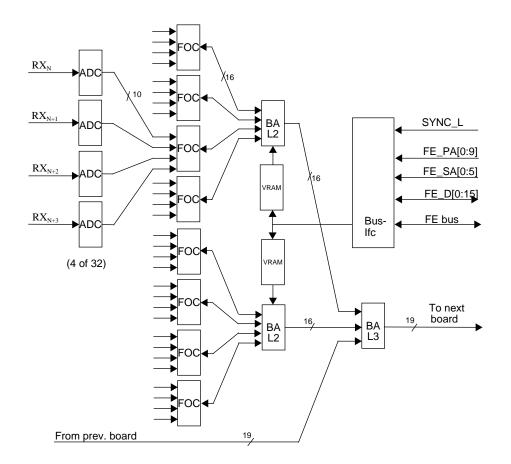

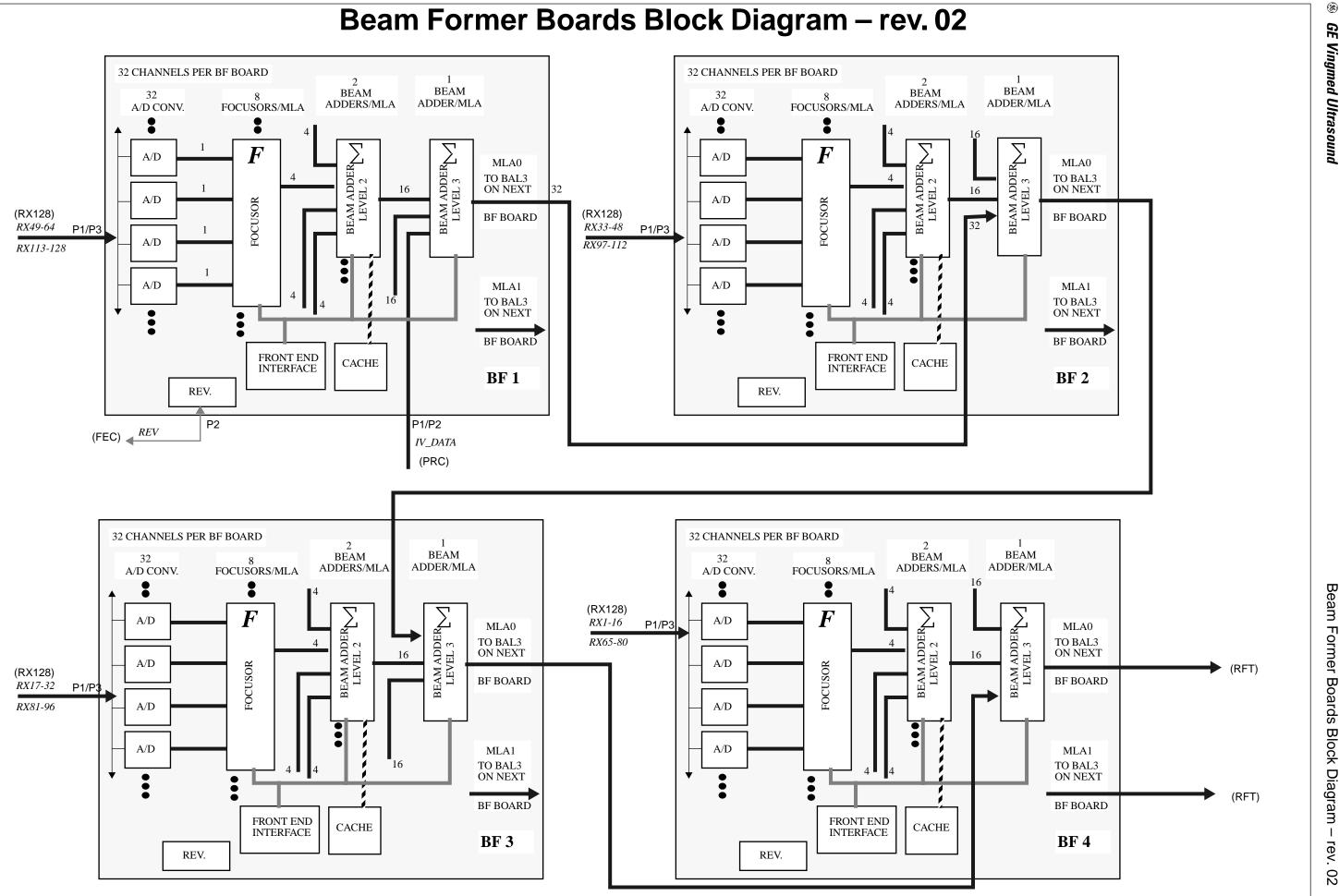

| Beam Former         | 27.0                | Overview                                                                    |        |

| Board - BF - rev.03 | 27.1                | Abstract                                                                    | -      |

|                     | 27.2                | Document History                                                            |        |

|                     | 27.3                | Nomenclature                                                                |        |

|                     | 28.0                | Inputs                                                                      |        |

|                     | <b>29.0</b><br>29.1 | Beam Former Board Functional Specification                                  |        |

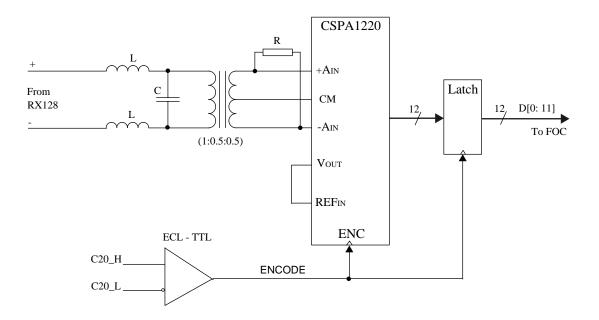

|                     | 29.2                | A/D Converter section                                                       | A2-42  |

|                     | 29.3                | Beamforming Section.                                                        | A2-43  |

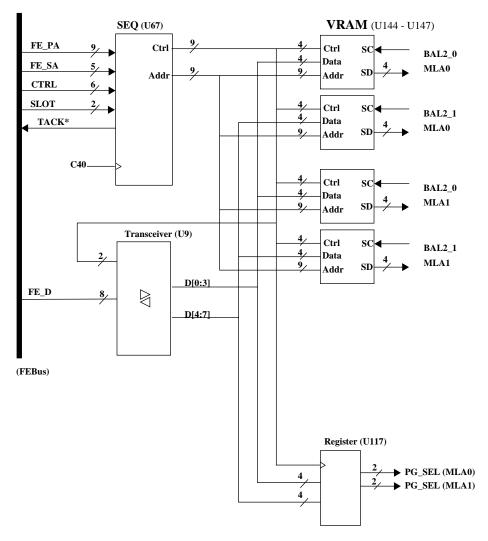

|                     | 29.4                | Video RAM and Parameter loading.                                            |        |

|                     | 29.5                | Clock Distribution.                                                         | A2-45  |

|                     | 29.6                | Front End Bus Interface                                                     | A2-45  |

|                     | 30.0                | Outputs                                                                     | A2-46  |

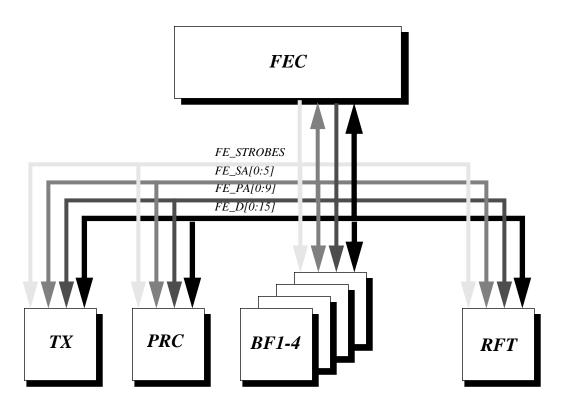

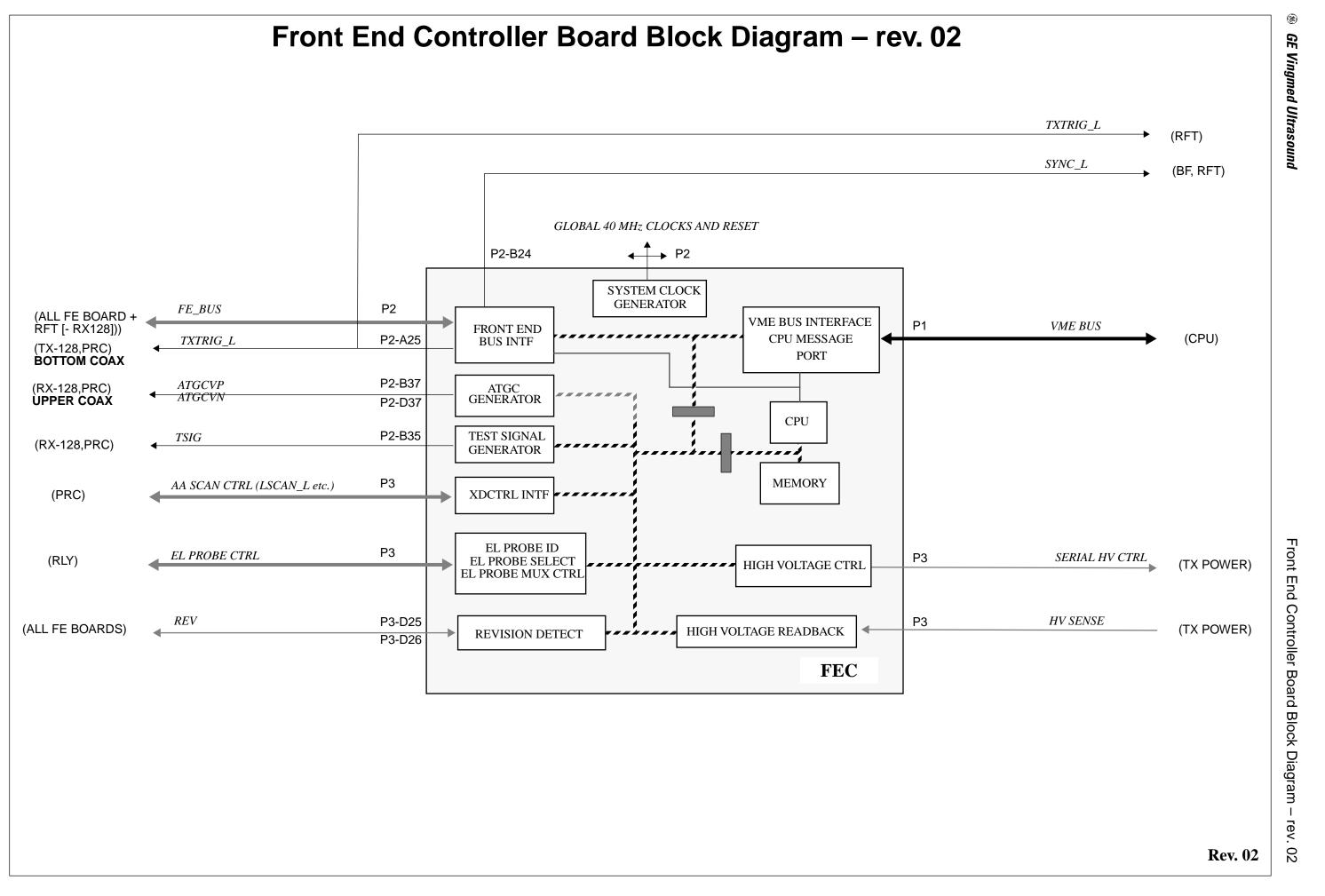

| Front End Control-  | 31.0                | Overview                                                                    |        |

| ler - FEC – rev. 04 | 31.1                | Abstract                                                                    |        |

|                     | 31.2                | Document History                                                            |        |

|                     | 31.3<br>31.4        | Definitions/Abbreviations/Nomenclature                                      |        |

|                     | -                   |                                                                             |        |

|                     | 32.0                | Inputs                                                                      |        |

|                     | <b>33.0</b><br>33.1 | Description           System Clock Generator                                |        |

|                     | 33.2                | Front End Bus Interface                                                     |        |

|                     | 33.3                | VME Bus Interface                                                           |        |

|                     | 33.3<br>33.4        | ATGC Generator                                                              |        |

|                     | 33.4<br>33.5        | Test Signal Generator                                                       |        |

|                     | 33.6                | XDCTRL Interface                                                            |        |

|                     | 33.0<br>33.7        | PA/LA Probe Select                                                          |        |

|                     | 33.8                | PA/LA Probe Identification                                                  |        |

|                     | 33.9                | LA Probe Multiplexer Select                                                 |        |

|                     | 33.10               | Revision Detect                                                             |        |

|                     |                     |                                                                             |        |

|                                              | Chapte                                                     | r Description                                                                                                                                  | Page #                           |

|----------------------------------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|                                              | 33.11<br>33.12<br>33.13                                    | AA and DP Probe Sense (from artwork F only)<br>Temperature Sensors (from artwork F only)                                                       | A2-50                            |

|                                              | <b>34.0</b><br>34.1                                        | Control                                                                                                                                        |                                  |

|                                              | 34.1                                                       | DSP                                                                                                                                            | -                                |

|                                              | 35.0                                                       | Outputs                                                                                                                                        | A2-52                            |

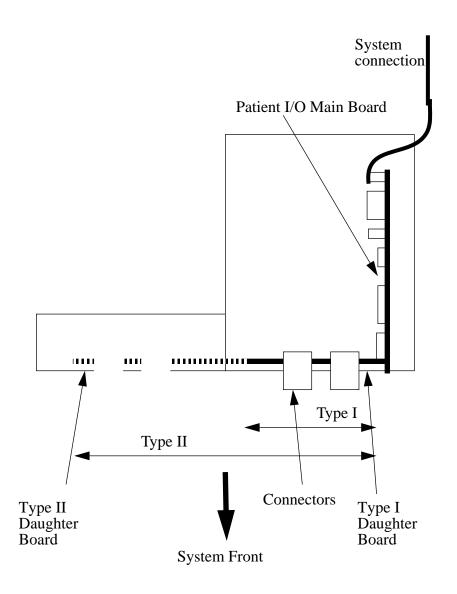

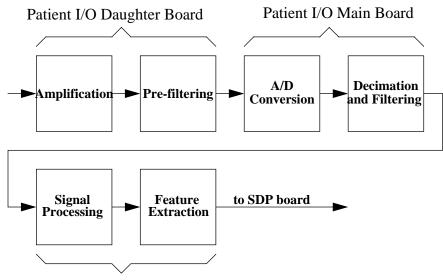

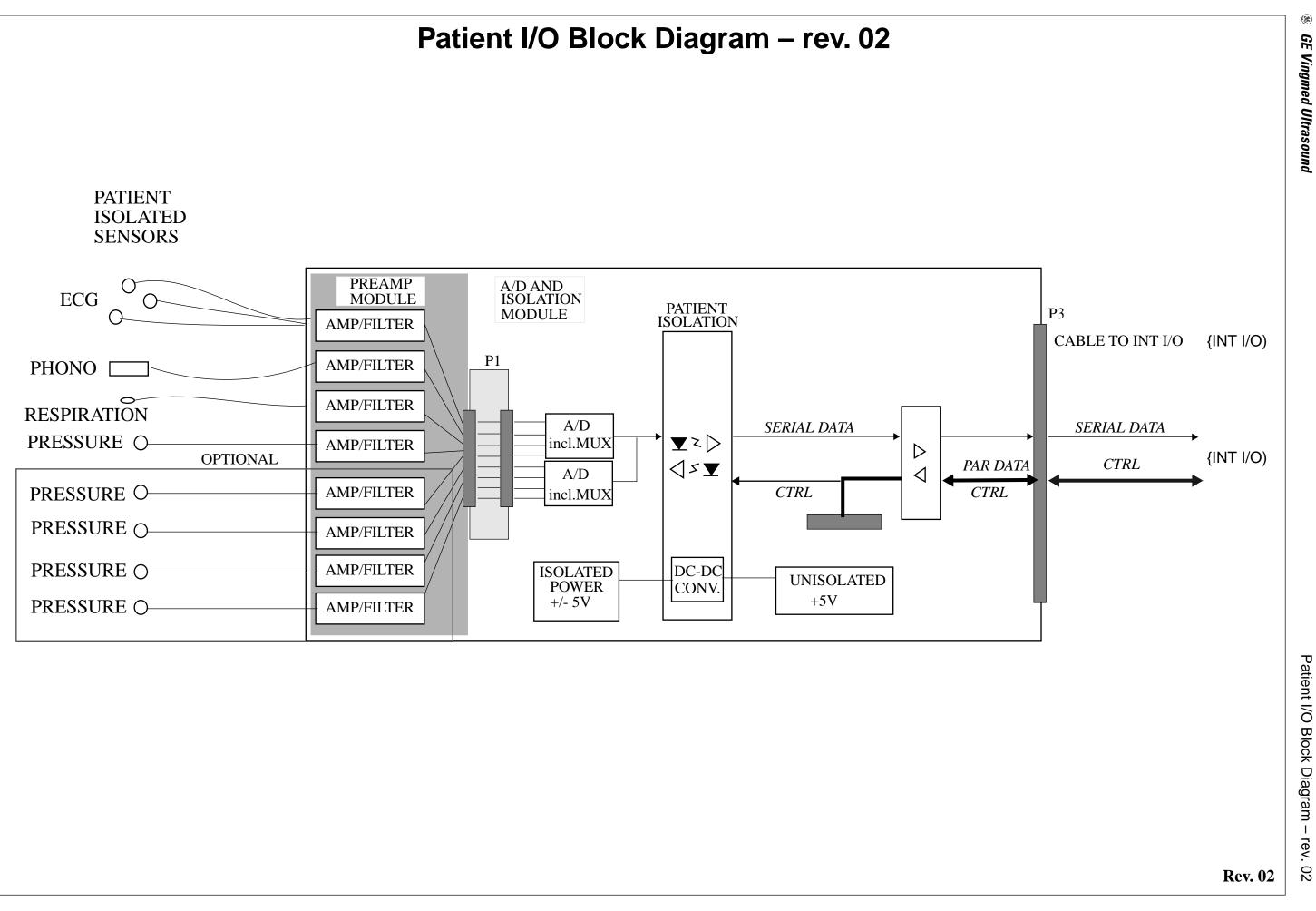

| Patient I/O rev.01                           | <b>36.0</b><br>36.1<br>36.2                                | Overview                                                                                                                                       | A2-53                            |

|                                              | 36.3                                                       | Definitions/Abbreviations/Nomenclature                                                                                                         |                                  |

|                                              | 36.4                                                       | References                                                                                                                                     |                                  |

|                                              | <b>37.0</b><br>37.1                                        | Mechanical Assembly                                                                                                                            | A2-53                            |

|                                              | 37.2                                                       | Daughter Boards                                                                                                                                |                                  |

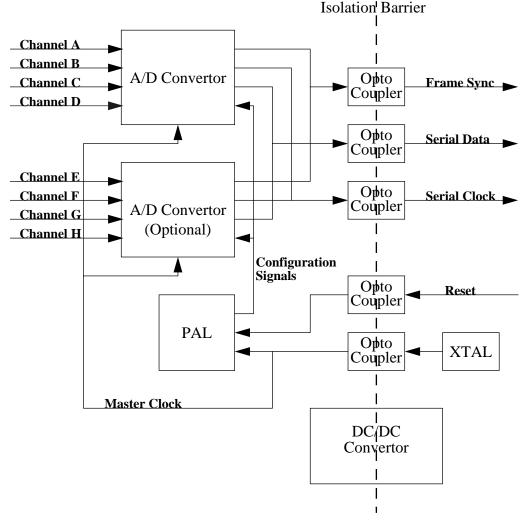

|                                              | <b>38.0</b><br><b>39.0</b><br>39.1<br>39.2<br>39.3         | Inputs Descriptions Overview Main Board ECG & Phono Board                                                                                      | A2-55<br>A2-55<br>A2-56          |

|                                              | 40.0<br>41.0                                               | Control                                                                                                                                        | A2-58                            |

| Transducer Bus<br>Board - XDBUS –<br>rev. 04 | <b>42.0</b><br>42.1<br>42.2<br>42.3<br>42.4<br><b>43.0</b> | Introduction         Abstract         Document History.         Definitions/Abbreviations/Nomenclature         References.         Description | A2-59<br>A2-59<br>A2-59<br>A2-59 |

#### **The Mid Processor Modules**

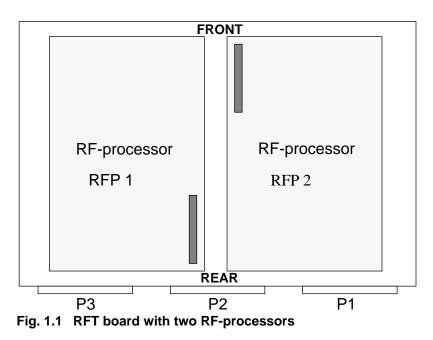

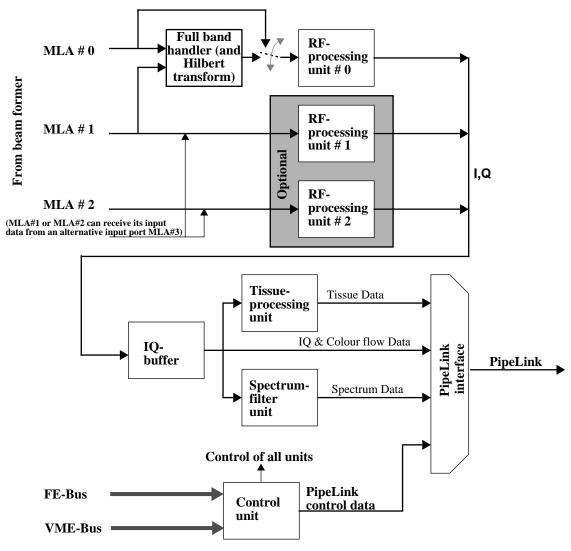

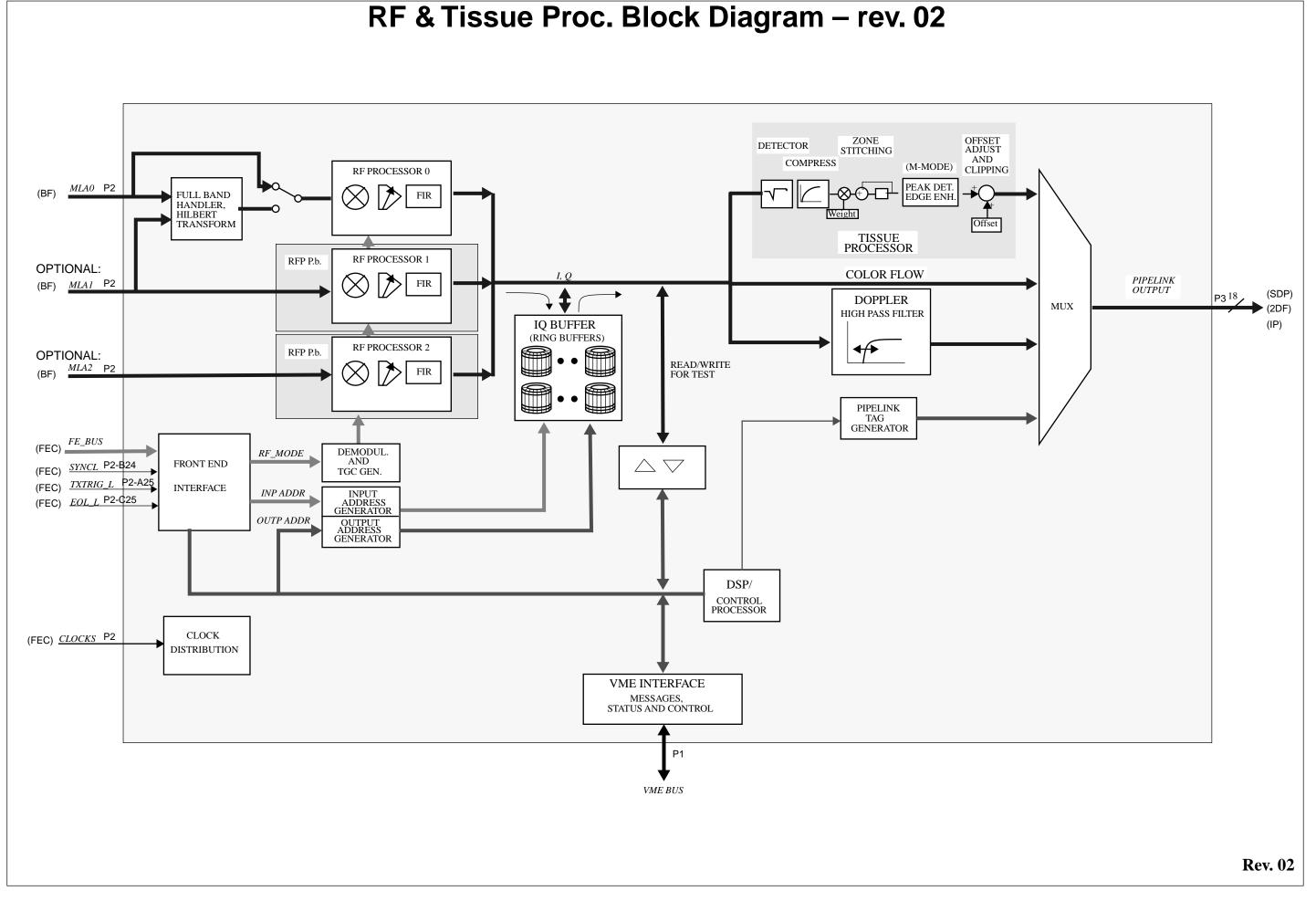

| RF- and Tissue  | 1.0 | Overview                                  | A3-3 |

|-----------------|-----|-------------------------------------------|------|

| Processor board | 1.1 | Abstract                                  | A3-3 |

|                 | 1.2 | Document History                          | A3-3 |

|                 | 1.3 | Definitions/Abbreviations/Nomenclature    | A3-3 |

|                 | 1.4 | References                                | A3-3 |

|                 | 1.5 | Mechanical specifications                 | A3-4 |

|                 | 2.0 | Inputs                                    | A3-4 |

|                 | 3.0 | Descriptions                              | A3-5 |

|                 | 3.1 | Full band handler (and Hilbert transform) |      |

|                 | 3.2 | RF-processing unit (RFP)                  | A3-6 |

|                 | 3.3 | IQ-buffer                                 | A3-6 |

|                 | 3.4 | Tissue Processing Unit                    | A3-6 |

|                 | 3.5 | Doppler High Pass Filter                  | A3-6 |

|                 | 3.6 | Local processor                           | A3-7 |

|                 | 4.0 | Control unit                              | A3-7 |

|                 | 5.0 | Connectors                                | A3-8 |

|                 | 5.1 | The RFT board                             | A3-8 |

|                 | 5.2 | The RFT1 board                            | A3-8 |

|                                         | Chapter                                                                                                                             | Description                                                                                                                                                                                                                                       | Page #                                                                    |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|                                         | <b>6.0</b><br>6.1                                                                                                                   | Outputs<br>PipeLink interface                                                                                                                                                                                                                     |                                                                           |

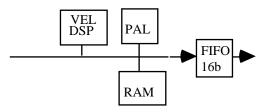

| Spectrum Doppler<br>Processor – rev. 03 | <b>7.0</b><br>7.1                                                                                                                   | Overview.                                                                                                                                                                                                                                         |                                                                           |

|                                         | 7.2                                                                                                                                 | Document History                                                                                                                                                                                                                                  |                                                                           |

|                                         | 7.3<br>7.4                                                                                                                          | Definitions/Abbreviations/Nomenclature                                                                                                                                                                                                            |                                                                           |

|                                         | <ul> <li>8.0</li> <li>9.0</li> <li>9.1</li> <li>9.2</li> <li>9.3</li> <li>10.0</li> <li>10.1</li> <li>10.2</li> <li>11.0</li> </ul> | Inputs         Descriptions.         Spectrum Analyzer         Audio and Missing Signal Estimation.         Digital-to-Analog Converter         Control         VME Interface         Master DSP Control and Administration Tasks         Outputs | . A3-10<br>. A3-10<br>. A3-11<br>. A3-11<br>. A3-11<br>. A3-11<br>. A3-11 |

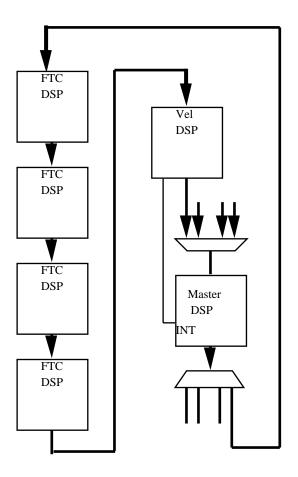

| 2D Flow Board -<br>rev.01               | <b>12.0</b><br>12.1<br>12.2<br>12.3<br>12.4                                                                                         | Overview                                                                                                                                                                                                                                          | . A3-12<br>. A3-12<br>. A3-12                                             |

|                                         | <b>13.0</b><br><b>14.0</b><br>14.1<br>14.2<br>14.3<br>14.4<br>14.5                                                                  | Inputs Descriptions General Description Input Dispatcher FTC DSPs VEL DSPs Master DSP                                                                                                                                                             | . A3-12<br>. A3-13<br>. A3-13<br>. A3-13<br>. A3-13<br>. A3-13            |

|                                         | <b>15.0</b><br>15.1<br>15.2<br><b>16.0</b>                                                                                          | Control                                                                                                                                                                                                                                           | . A3-14<br>. A3-14<br>. A3-15                                             |

#### The Display and Control System

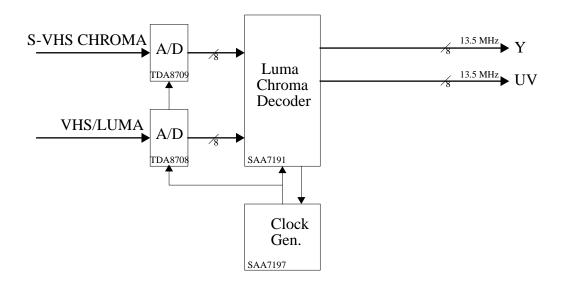

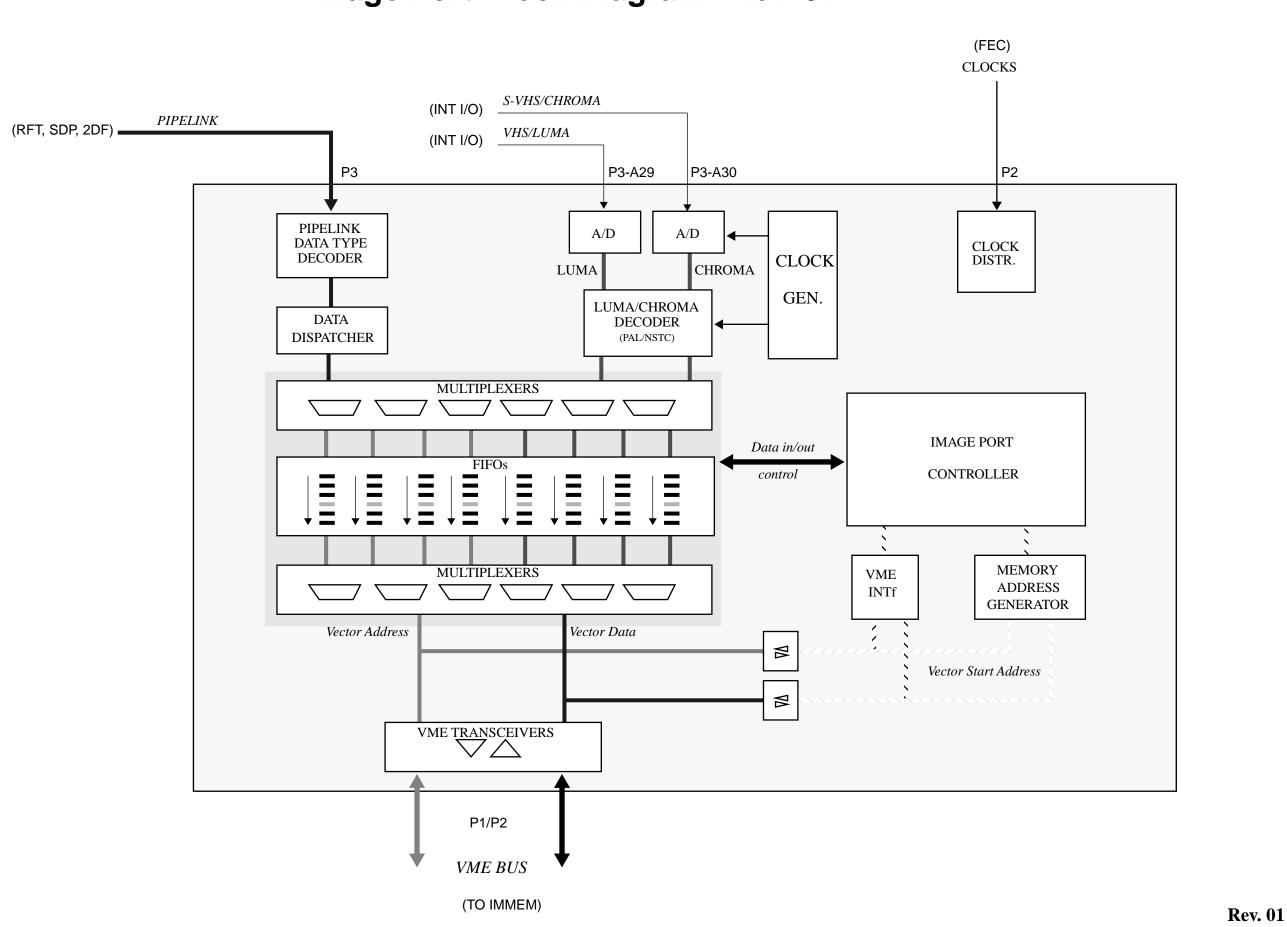

| Image Port Board -<br>rev. 02 | <b>1.0</b><br>1.1        | <b>Overview</b>                                                             |

|-------------------------------|--------------------------|-----------------------------------------------------------------------------|

|                               | 1.2                      | Revision History A4-3                                                       |

|                               | 1.3                      | Definitions/Abbreviations/Nomenclature A4-3                                 |

|                               | 1.4                      | References A4-3                                                             |

|                               | <b>2.0</b><br>2.1<br>2.2 | Inputs                                                                      |

|                               |                          | Video input A4-3                                                            |

|                               | <b>3.0</b><br>3.1        | Descriptions         A4-4           Pipelink Data Type Decoder         A4-4 |

|                               | 3.2                      | Video A/D conversion and decoding A4-4                                      |

|                               | 3.3                      | FIFO buffers                                                                |

|                               | 3.4                      | Image Port Controller A4-4                                                  |

|                               | <b>4.0</b><br>4.1        | Outputs A4-5<br>Output to Image Memory A4-5                                 |

|                                  | Chapter                                                                                                                                                                                                                                                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page #                                                                                                                                                       |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

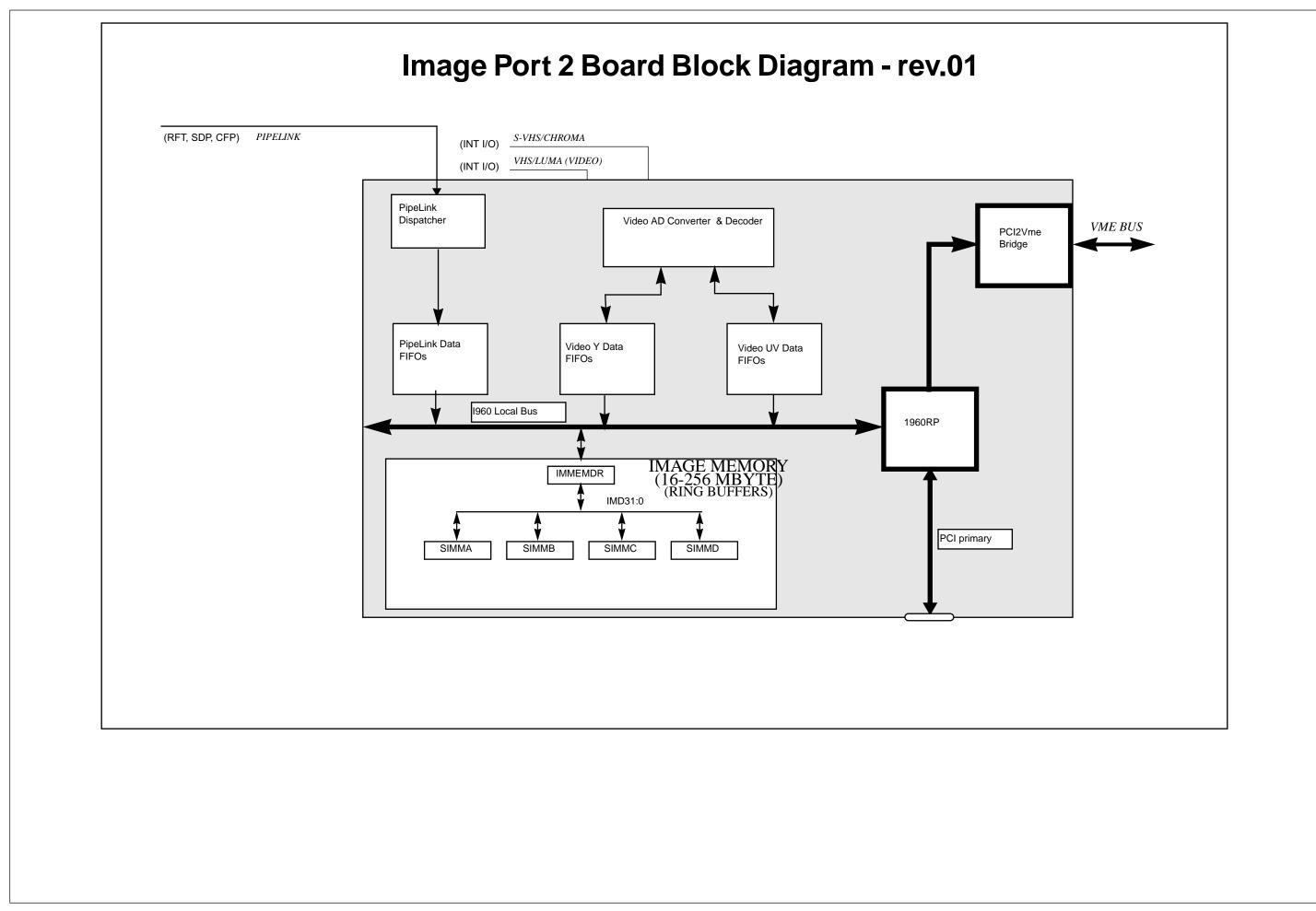

| Image Port 2 Board<br>- rev. 01  | <ul> <li><b>5.0</b></li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li><b>6.0</b></li> <li>6.1</li> <li>6.2</li> <li><b>7.0</b></li> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> <li><b>8.0</b></li> <li>8.1</li> </ul> | Overview         Abstract         Revision History         Definitions/Abbreviations/Nomenclature         References         Inputs         PipeLink input.         Video input         Scanner Dataflow         Video Dataflow         Mixed Scanner/Video Input Dataflow         Data Set Ring Buffers         Video Input         FIFO buffers.         Output to Image Memory         Dataflow Control Description         Input Flow Decode / Capture | A4-6<br>A4-6<br>A4-6<br>A4-6<br>A4-6<br>A4-6<br>A4-6<br>A4-6<br>A4-6<br>A4-7<br>A4-7<br>A4-7<br>A4-7<br>A4-7<br>A4-8<br>A4-8<br>A4-9<br>A4-9<br>A4-9<br>A4-9 |

| Image Memory<br>board - rev. 03  | 8.2<br>9.0<br>9.1<br>9.2<br>9.3<br>9.4<br><b>10.0</b><br>10.1<br>10.2<br>10.3<br>10.4<br>10.5                                                                                                                                                                                    | Output Flow Control         Introduction         Abstract         Document History.         Definitions/Abbreviations/Nomenclature         References.         Descriptions         General         Memory Size         Address Decoding         Parity Control         Referesh.                                                                                                                                                                          | A4-10<br>A4-10<br>A4-10<br>A4-10<br>A4-10<br>A4-10<br>A4-10<br>A4-10<br>A4-11<br>A4-11                                                                       |

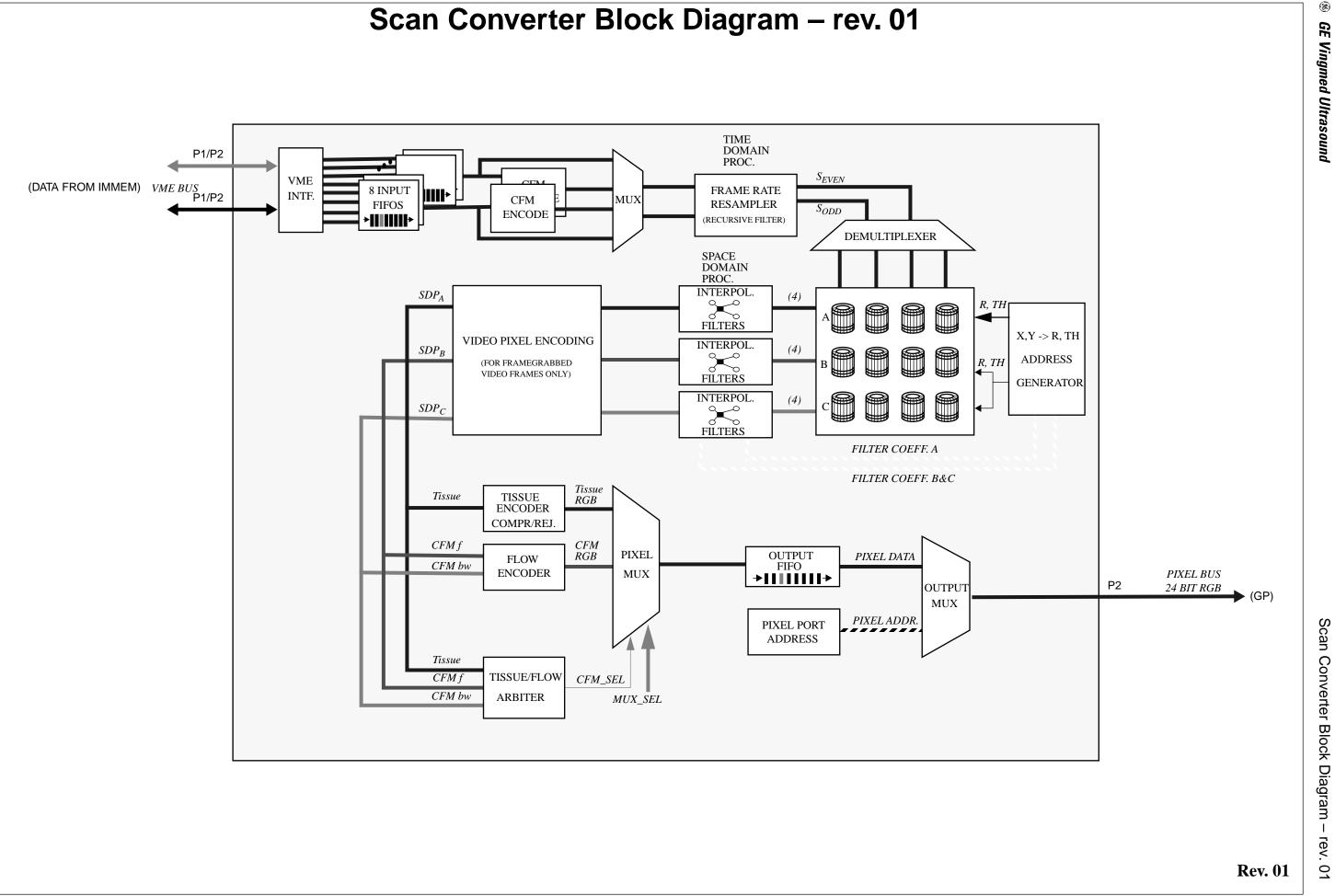

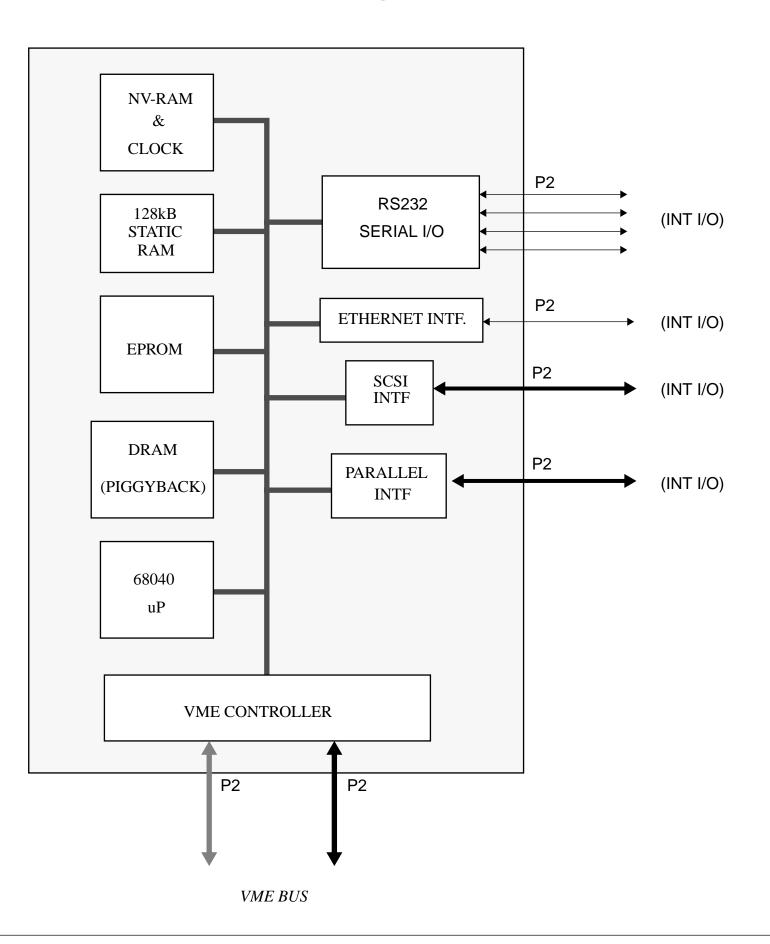

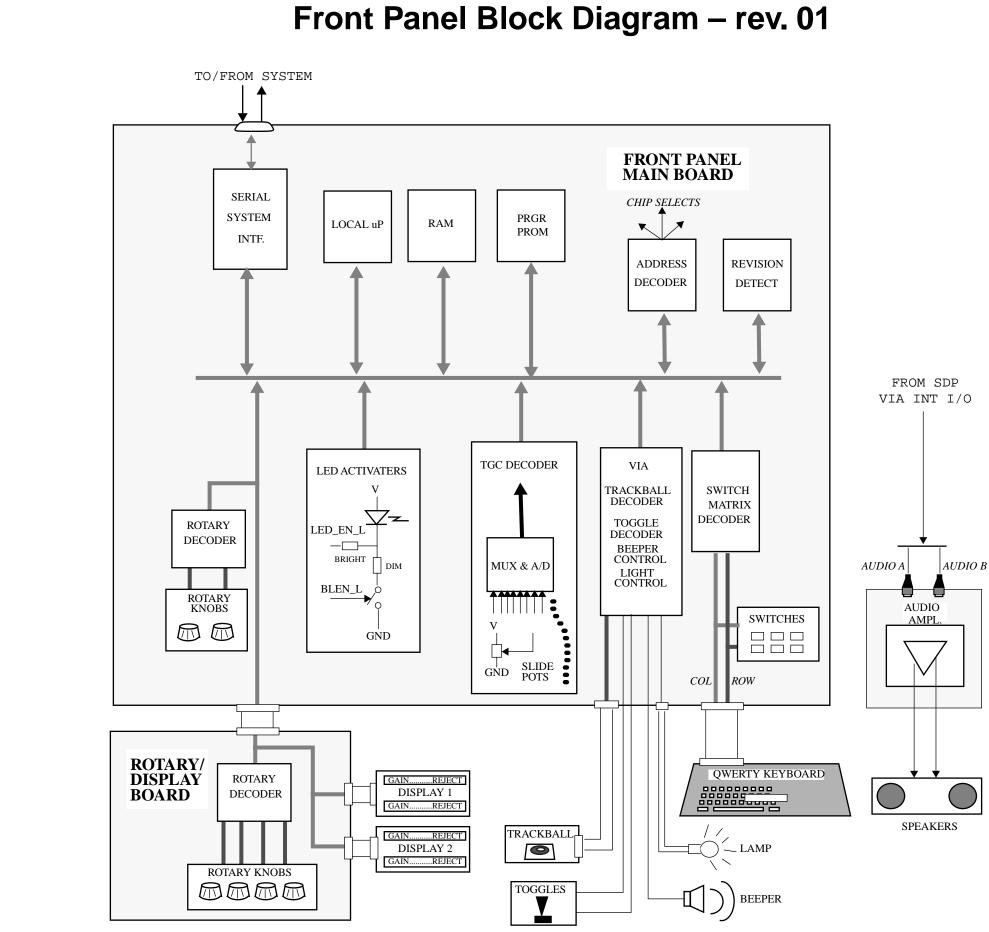

| Scan Converter<br>Board - rev.01 | <ul> <li>11.0</li> <li>11.1</li> <li>11.2</li> <li>11.3</li> <li>11.4</li> <li>12.0</li> <li>13.0</li> <li>13.1</li> <li>13.2</li> <li>13.3</li> <li>13.4</li> <li>14.0</li> <li>15.0</li> <li>15.1</li> </ul>                                                                   | Overview .<br>Abstract .<br>Document History.<br>Definitions/Abbreviations/Nomenclature .<br>References.<br>Inputs .<br>Descriptions .<br>Time Domain Processor.<br>Space Domain Processor .<br>Pixel Encoding .<br>Pixel Port Interface.<br>Control .<br>Outputs .<br>Pixel Bus .                                                                                                                                                                         | A4-12<br>A4-12<br>A4-12<br>A4-12<br>A4-12<br>A4-12<br>A4-13<br>A4-13<br>A4-13<br>A4-14<br>A4-14<br>A4-14                                                     |

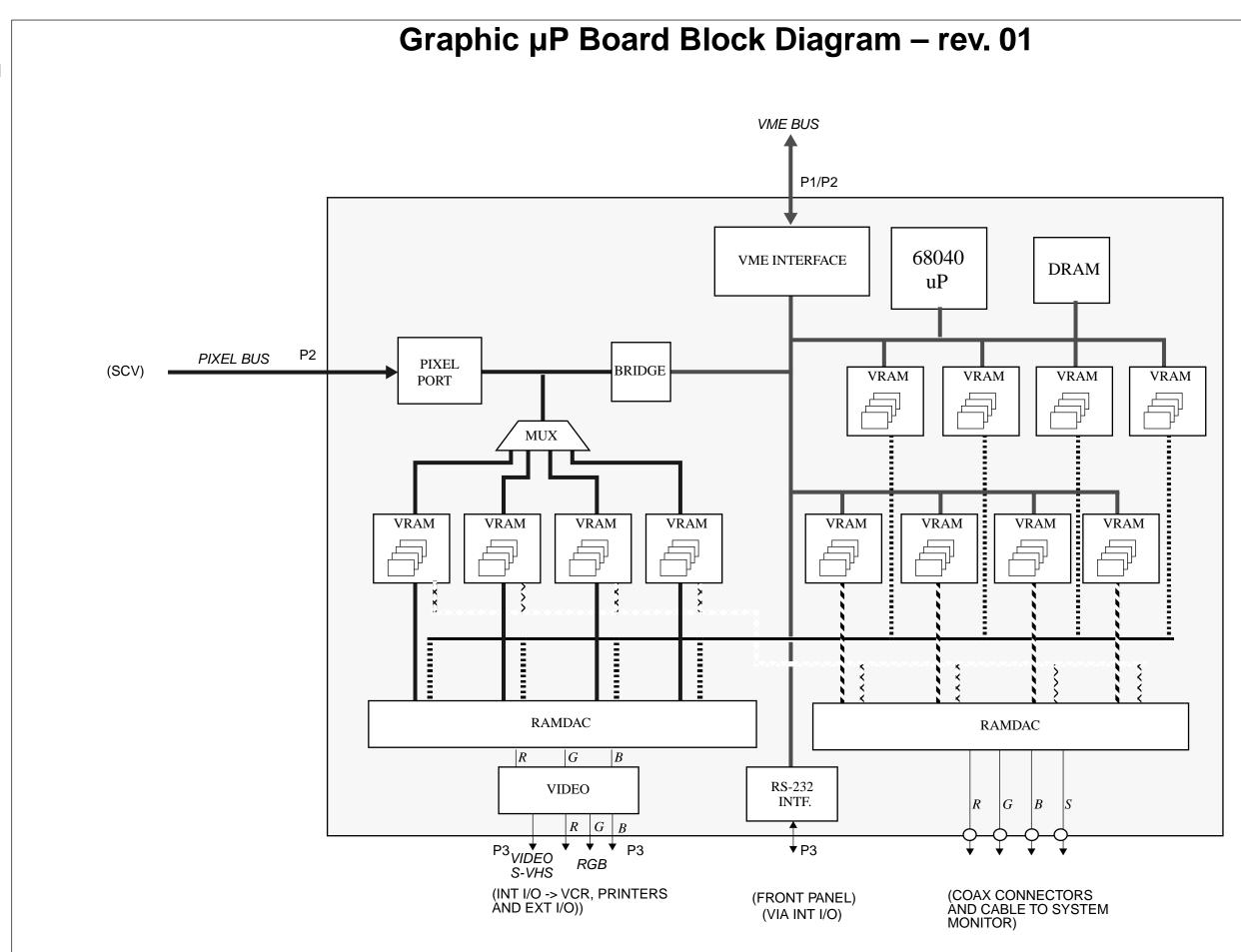

| Graphic Processor<br>- rev.01    | <b>16.0</b><br>16.1<br>16.2<br>16.3<br>16.4                                                                                                                                                                                                                                      | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                               | A4-15<br>A4-15<br>A4-15                                                                                                                                      |

|                    | Chapte                                                                                                                     | er Description                                                                                                                                                                                                                                                                                              | Page #                                                                                                                           |

|--------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

|                    | <b>17.0</b><br>17.1<br>17.2<br>17.3<br>17.4                                                                                | Descriptions         Pixel port         Video RAMs         VME Interface         X-server                                                                                                                                                                                                                   | . A4-16<br>. A4-16<br>. A4-16<br>. A4-16                                                                                         |

|                    | 17.5<br>17.6<br>17.7<br>17.8                                                                                               | RAMDAC and RGB outputs         Video and S-VHS outputs         Serial Interfaces         MC68040 uP                                                                                                                                                                                                         | . A4-16<br>. A4-16                                                                                                               |