# medison mysono201 ultrasound system

# **SERVICE MANUAL VER 1.0**

# **CONTENTS**

# A TABLE OF CONTENTS

#### Section 1. Basic Information

- 1. What is Mysono201?

- 2. Mysono201 Configuration

- 2.1 Main body

- 2.2 Monitor

- 2.3 Probe

- 2.4 Accessory

- 2.5 peripheral unit (Option)

# 3. Safety precautions

- 3.1 Safety standard

- 3.2 Electrical safety

- 3.2.1 Protection of equipment

- 3.2.2 Battery safety

- 3.2.3 Symbol

- 3.3 Physical safety

- 3.4 Maintenance and cleaning

- 3.4.1 Probe

- 3.4.1.1 Cleaning

- 3.4.1.2 Disinfection and Sterilization

- 3.4.2 Biopsy guide adapter and Needle guide

- 3.4.2.1 Stainless biopsy guide cleaning

- 3.4.2.2 Stainless biopsy guide sterilization

- 3.4.2.3 Plastic biopsy guide cleaning

- 3.4.2.4 Plastic biopsy guide sterilization

- 3.4.3 The surface of equipment

- 3.4.1 Cleaning

- 3.4.2 Sterilization

#### 4. Mysono201 installation

- 4.1 Probe setting and removing

- 4.2 Battery setting and removing

- 4.3 Battery charging and discharging

- 4.4 System power ON / OFF

- 4.5 Using AC adapter

#### 5. Mysono201 Function

Mysono201 Precautions Check List

# A TABLE OF CONTENTS

# Section 2. Description of System

#### 1.System Block Diagram

#### 2. Front End Board (F/E)

- 2.1 General Description

- 2.2 Block Diagram

- 2.3 Signal Definition

- 2.3.1 CPLD Signal Definition

- 2.3.2 Connector signals between DSC and FE

- 2.3.3 Connector signals between Power and FE

- 2.3.4 Connector signals between FE Adapter and FE

- 2.3.5 Connector signals between FE Adapter and SPC(System Probe Connector)

- 2.3.6 Connector signals between SPC(System Probe Connector) and Probe

- 2.4 Scanline Definition

- 2.4.1 Normal Mode

- 2.4.2 Synthetic Mode

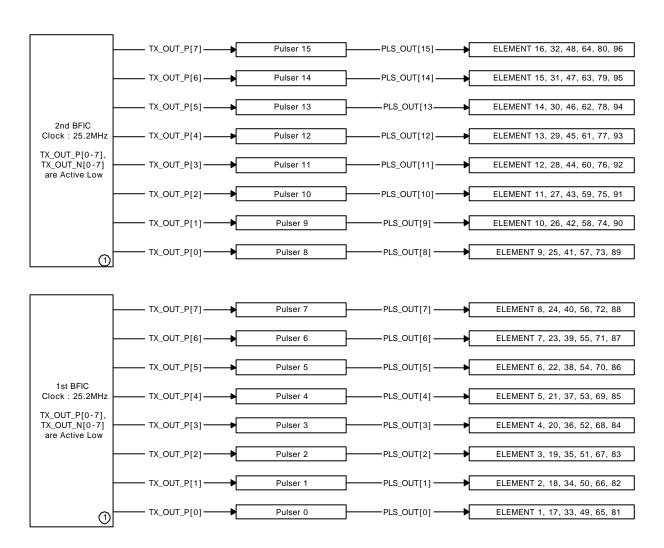

- 2.5 Pulser vs Elements

- 2.6 Specific Description

- 2.6.1 TGC Amp

- 2.6.2 Reordering

- 2.6.3 LPF

- 2.6.4 Beamforing IC MCB014A

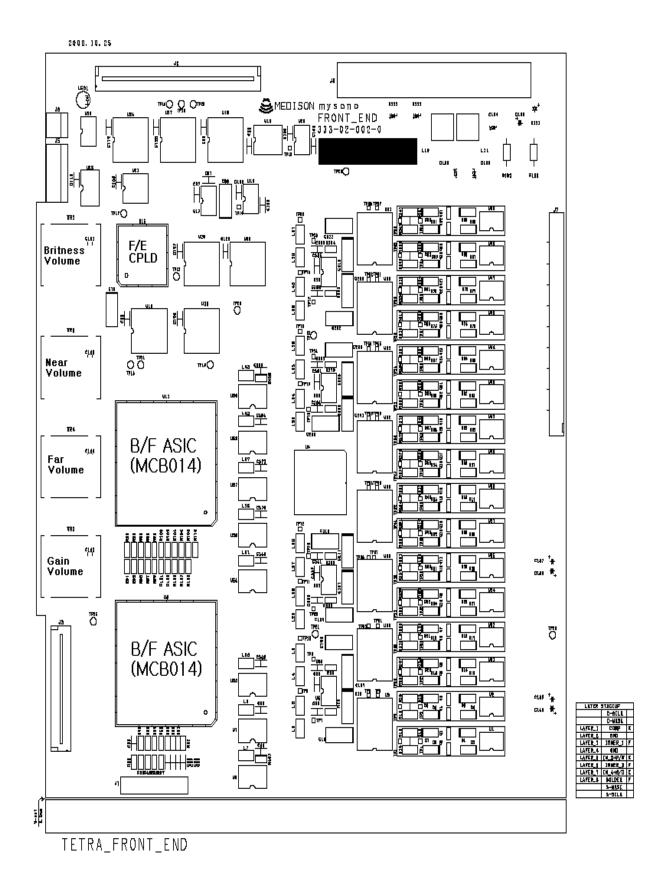

- 2.7 PCB Board Lay Out

- 2.7.1 F/E Top Side

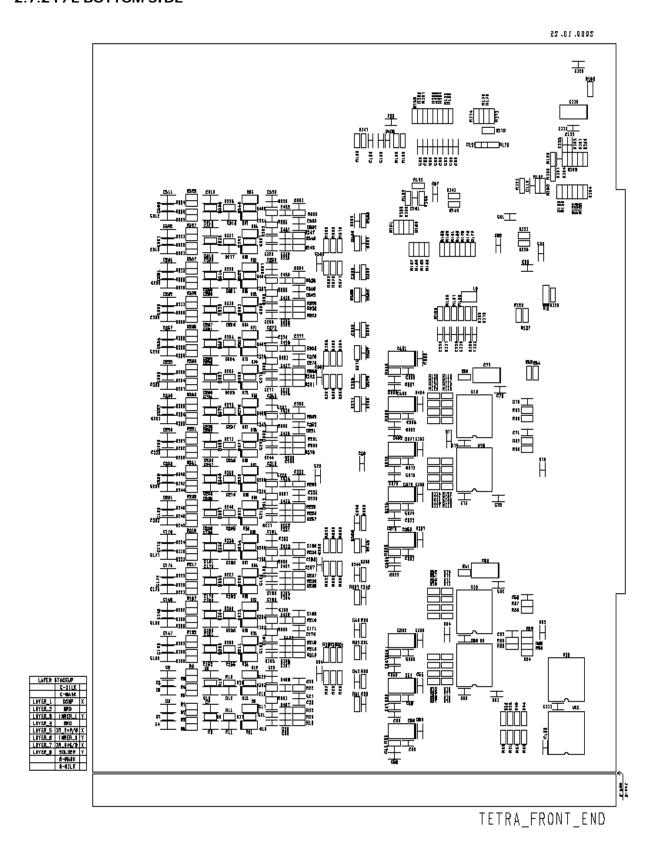

- 2.7.2 F/E Bottom Side

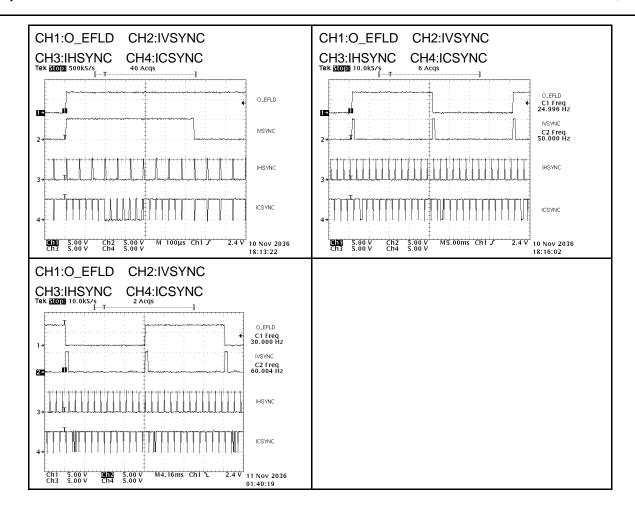

- 2.8 Timing Chart

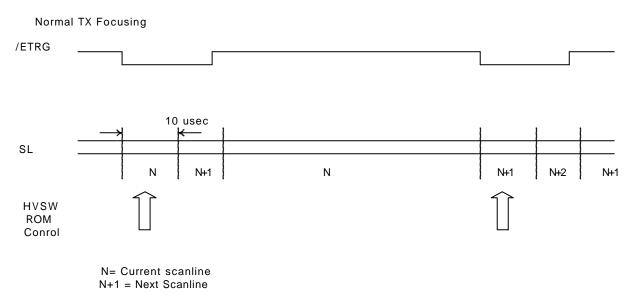

- 2.8.1 Normal TX Focusing

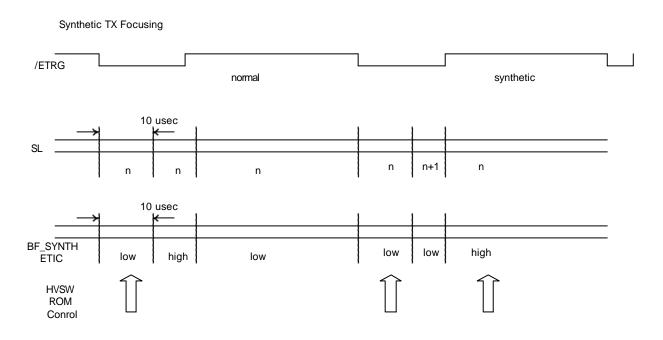

- 2.8.2 Synthetic TX Focusing

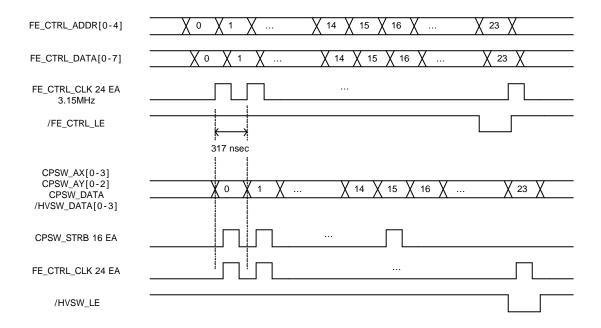

- 2.8.3 Control Timing

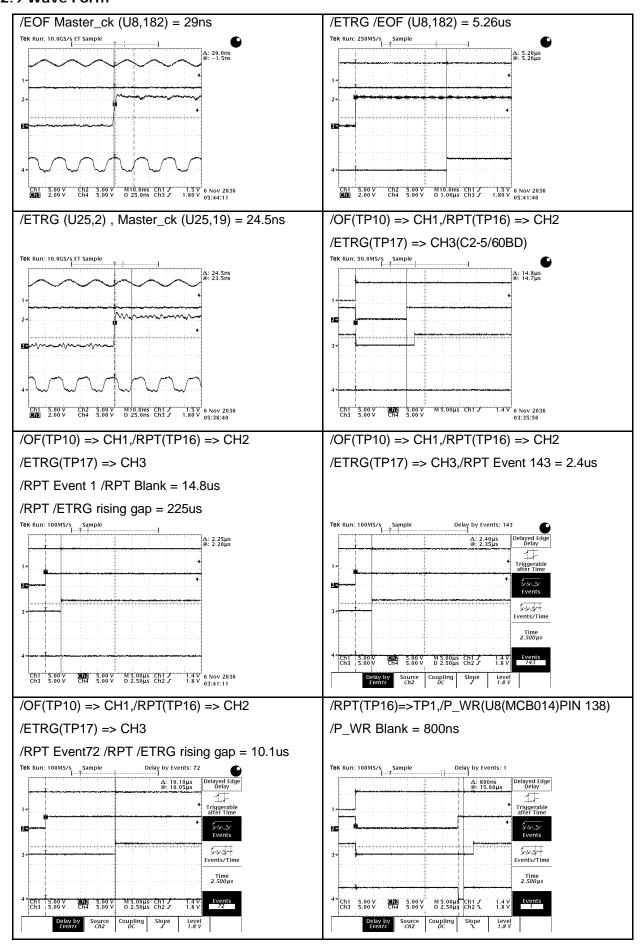

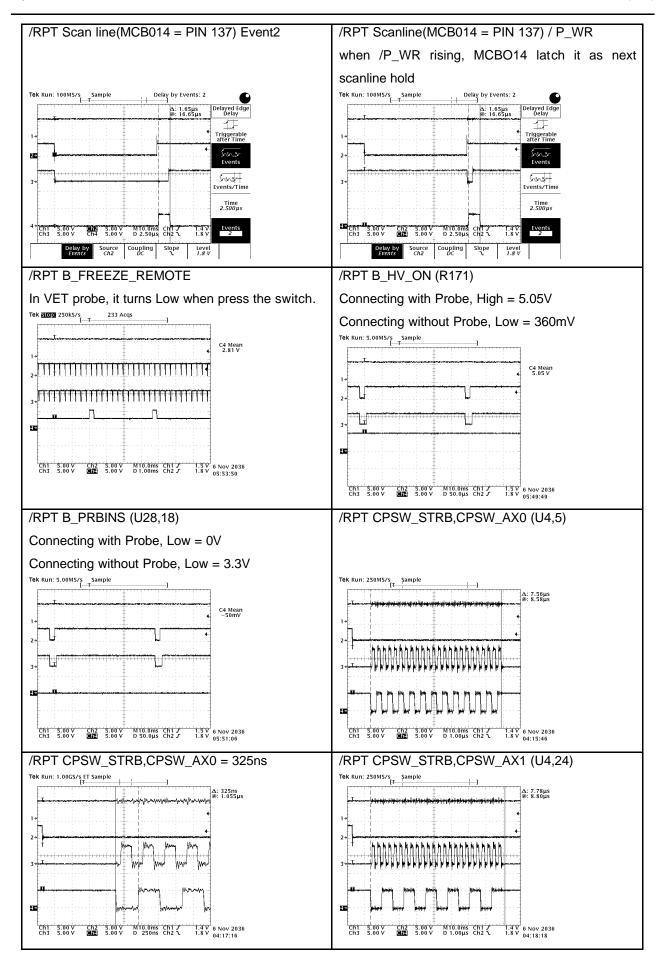

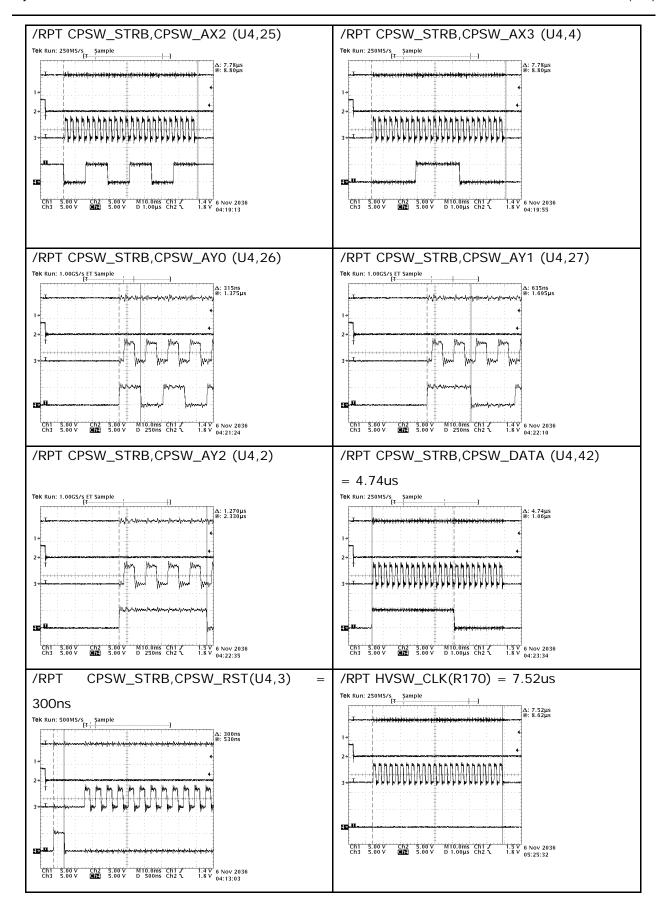

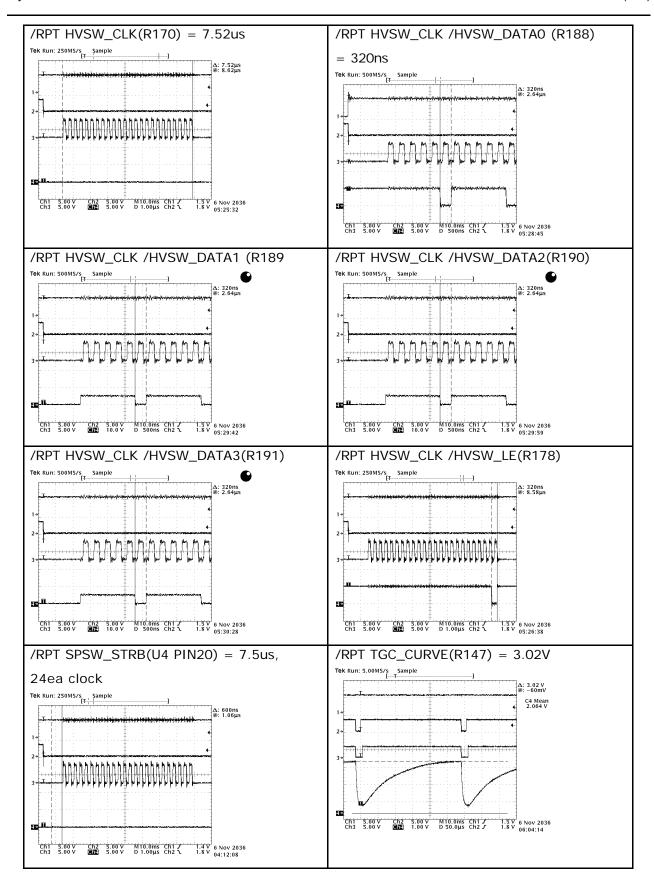

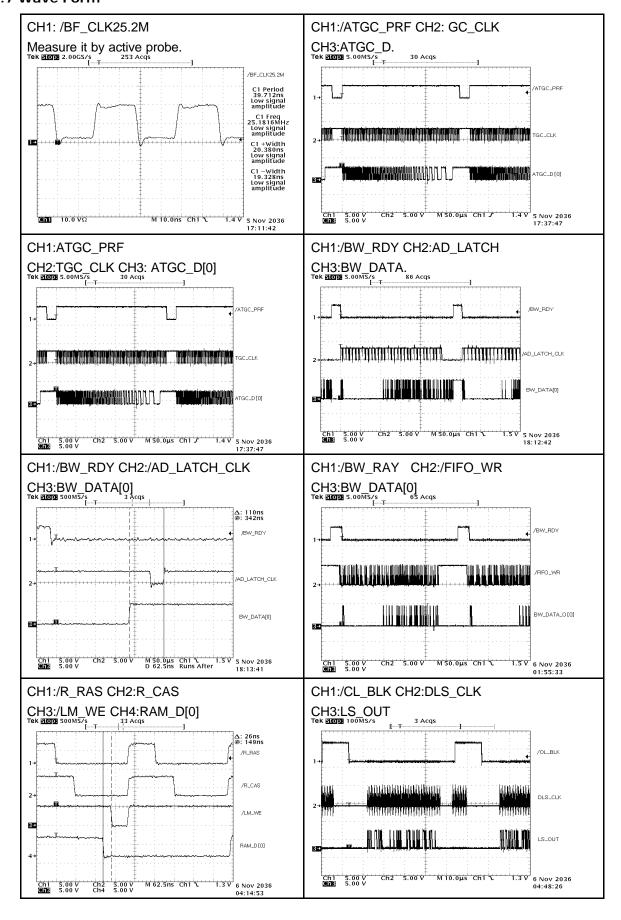

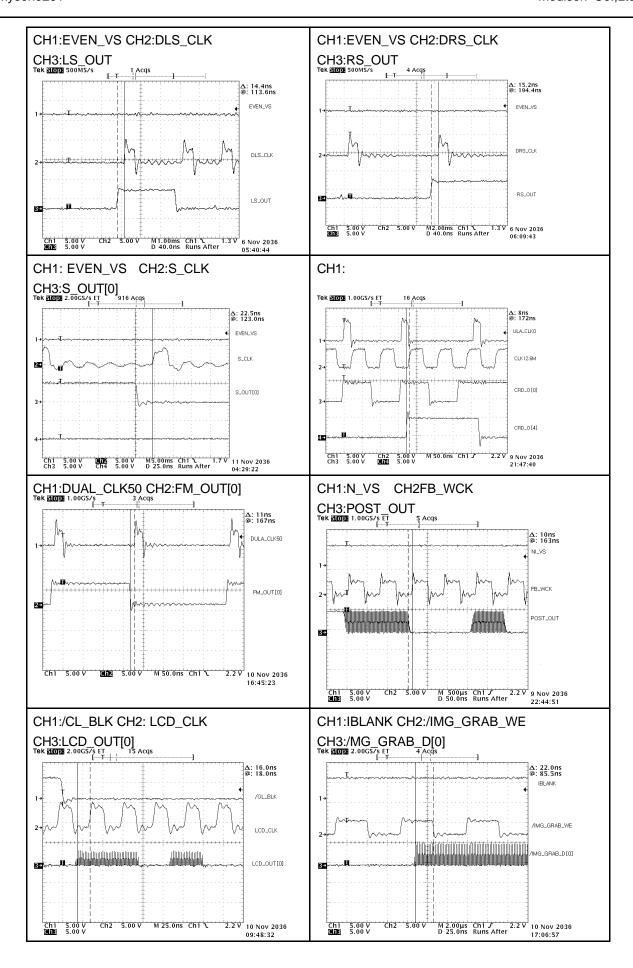

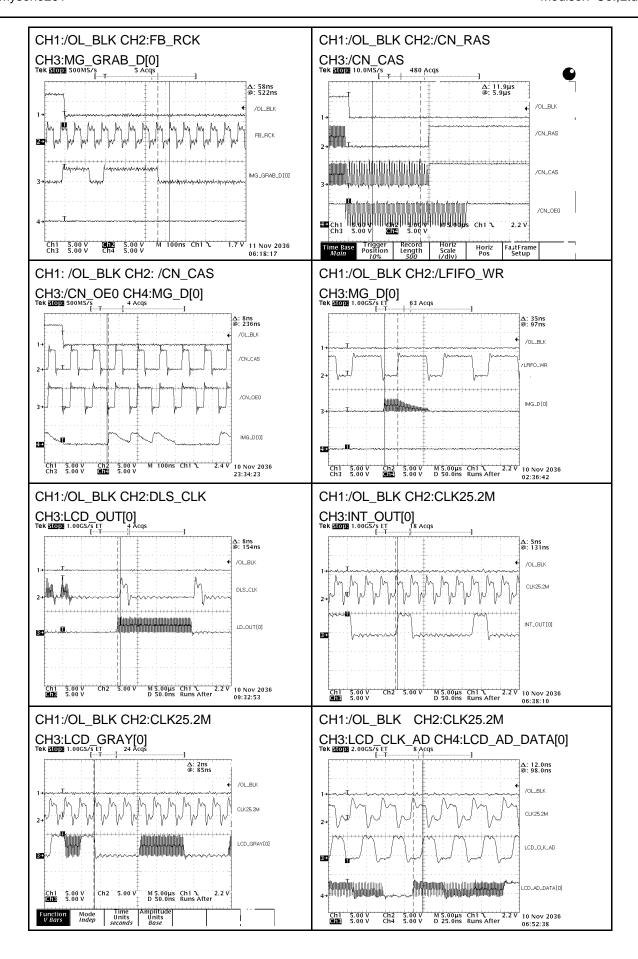

- 2.9 Wave Form

#### 3.DSC Board

- 3.1. Description Overall

- 3.2. Block Diagram

- 3.3 Signal Definition

- 3.4 Specification explain

- 3.4.1 B/W Data Receiving & FM storing Part

- 3.4.1.1 Mid Processor (MGA015)3.4 Specification explain

# A TABLE OF CONTENTS

# Section 2. Description of System

- 3.4.1.2 Pattern generator

- 3.4.1.3 Before FM controller (MGA001)

- 3.4.1.4 FM controller (MGA001)

- 3.4.2 Frame Memory & Cine Memory Flash Memory Part

- 3.4.2.1 Frame Memory (VRAM)

- 3.4.2.2 Cine Memory (DRAM)

- 3.4.2.3 Flash Memory

- 3.4.2.4 Memory Path by mode

- 3.4.2.5 Scanline Masking Window

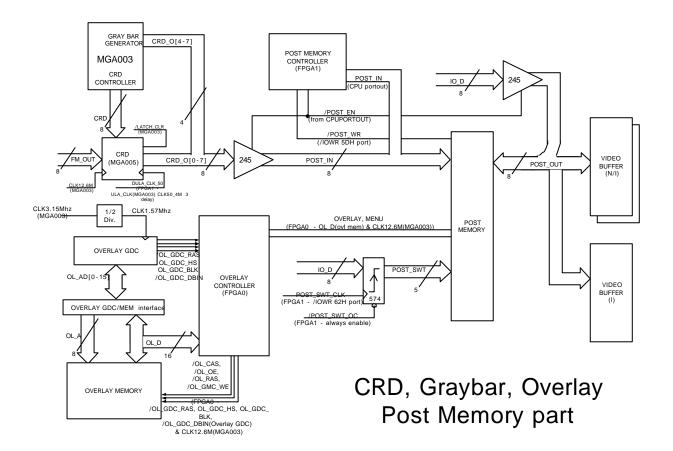

- 3.4.3 CRD, Graybar, Overlay Post Memory Part

- 3.4.3.1 CRD

- 3.4.3.2 Graybar

- 3.4.3.3 Overlay

- 3.4.3.4 Overlay Control Scheme

- 3.4.3.5 Post Memory

- 3.4.4 Non interlace Output Display Path part

- 3.4.4.1 Function

- 3.4.4.2 VGA

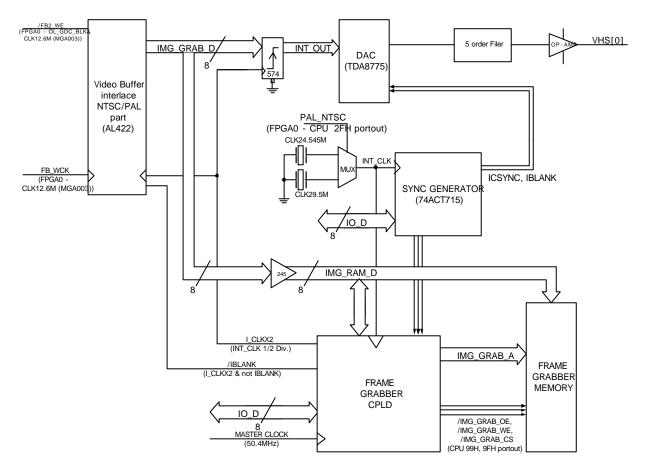

- 3.4.4.3 VHS

- 3.4.4.3.1 74ACT715 control

- 3.4.4.4 Non Interlaced B/W (NI B/W)

- 3.4.5 Interlace TSC/PAL Display Part

- 3.4.5.1 Frame Grabber CPLD & Memory

- 3.5 PCB Board Lay Out

- 3.5.1 DSC Top Side

- 3.5.2 DSC Bottom Side

- 3.6 Timing Chart

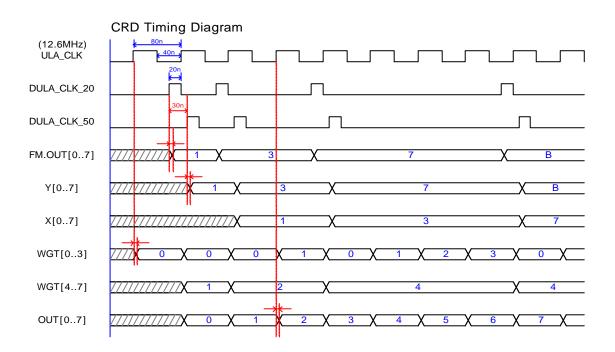

- 3.6.1 CRD Timing Chart

- 3.7 Wave Form

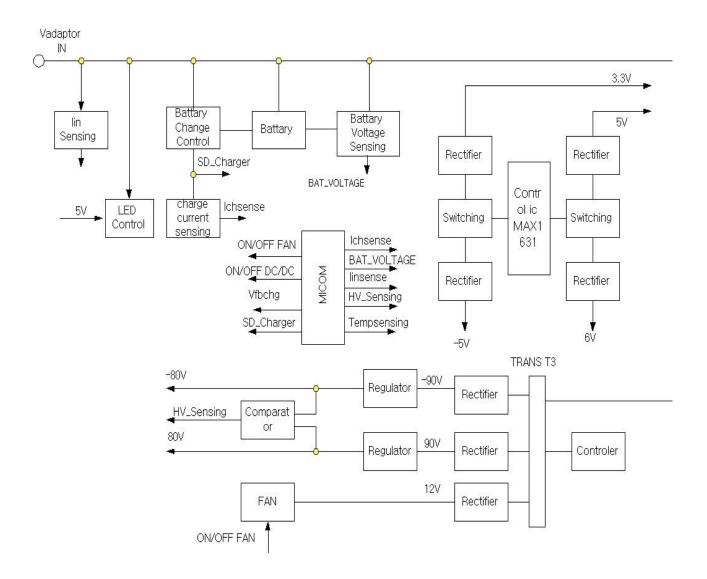

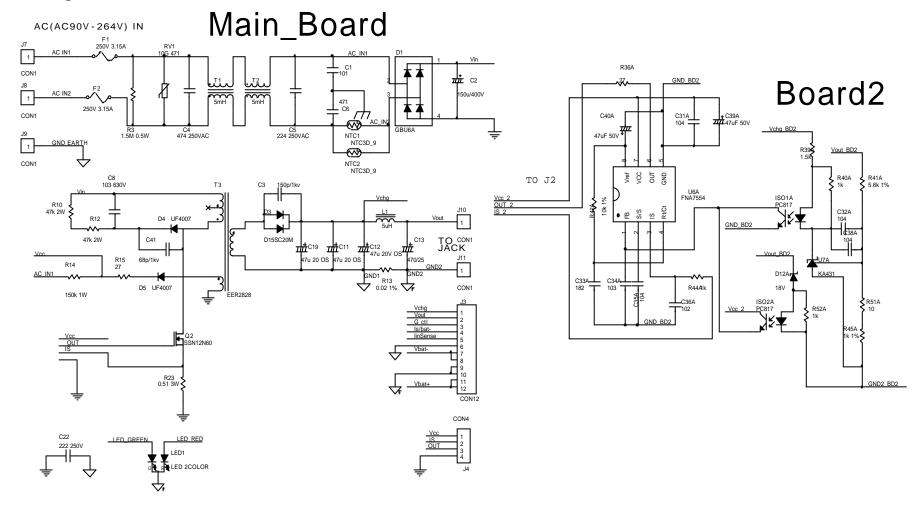

#### 4. Power B/D

- 4.1 Specification

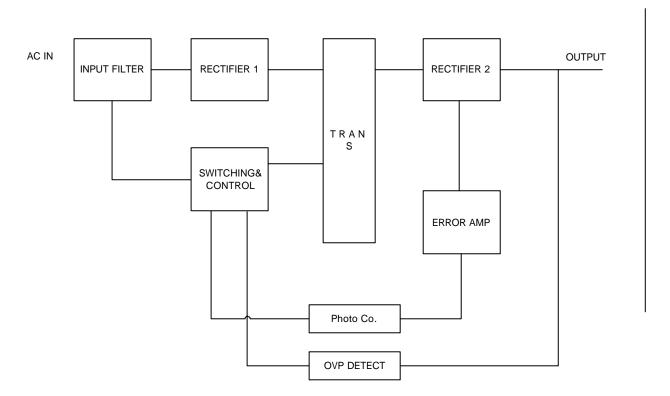

- 4.2 Block Diagram

- 4.3 Specification explain

#### 5.Probe

5.1.General Description

# A TABLE OF CONTENTS

# Section 2. Description of System

- 5.2. Specification explain

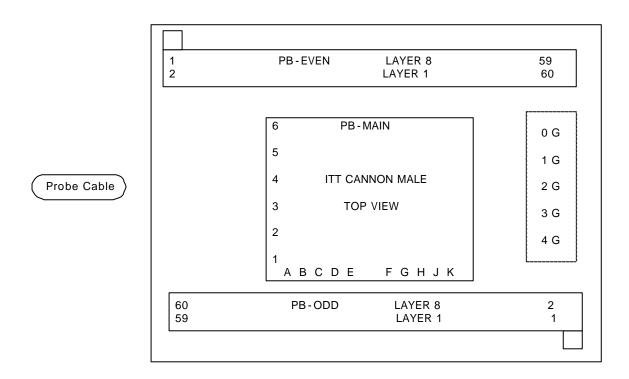

- 5.3 Probe Connector Pin Define

- 5.4 Signal Definition

- 5.5 Probe ID

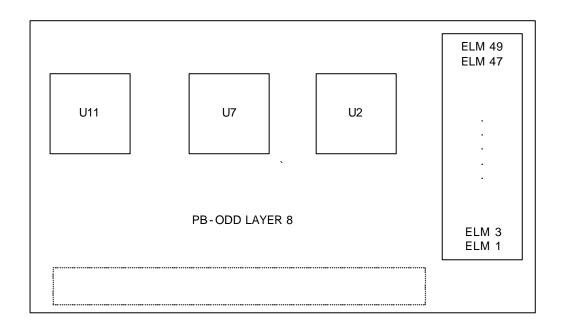

- 5.6 PCB Lay Out

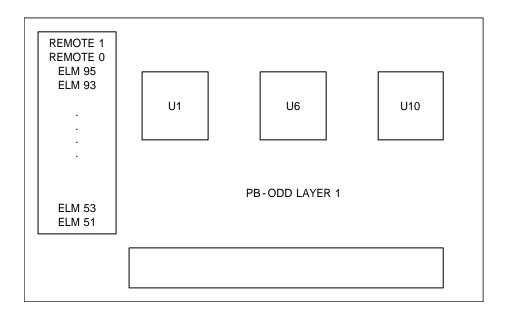

- 5.6.1 PB Main Top Side

- 5.6.2 PB\_ODD Top/Bottom Size

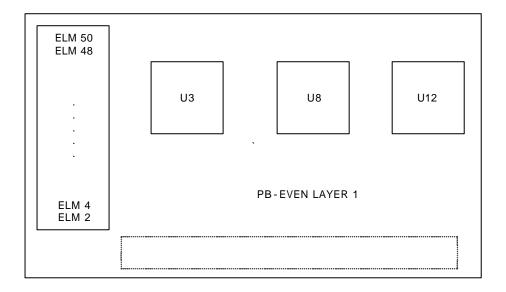

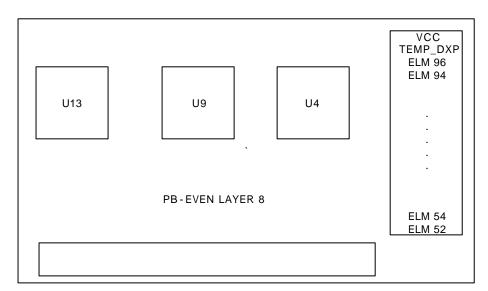

- 5.6.3 PB\_EVEN Top/Bottom Size

#### **6.ASIC Data Sheet**

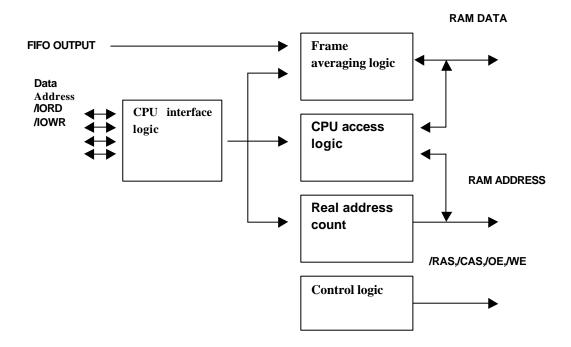

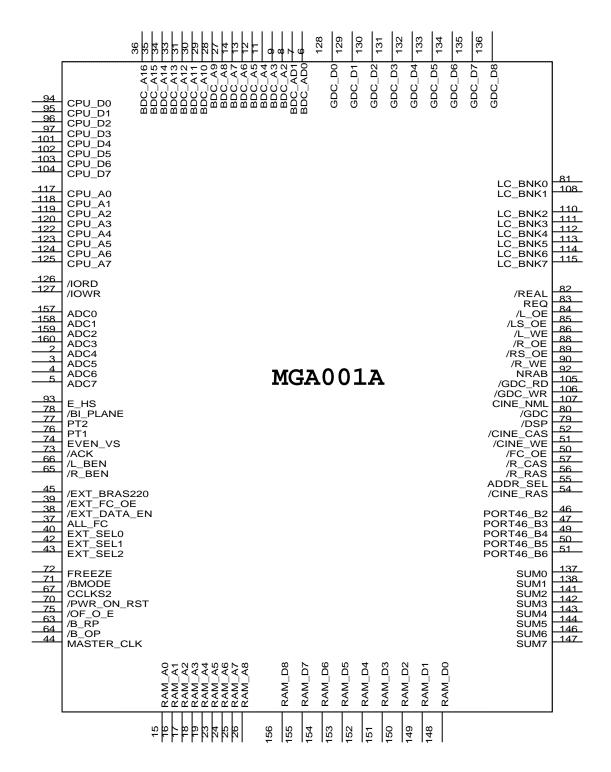

- 6.1 MAGA0010A Manual (draft): Frame Memory Controller

- 6.1.1 Description

- 6.1.1 Description

- 6.1.3 PIN Diagram

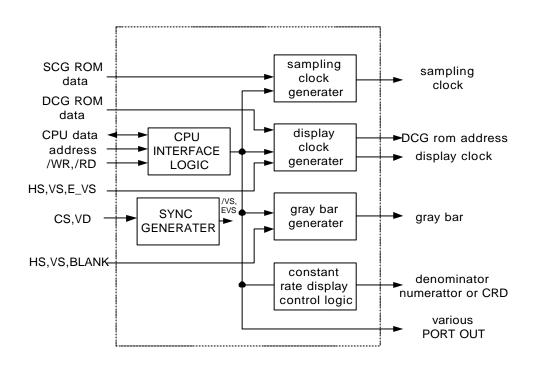

- 6.2 MAGA003A Manual (draft): Clocks Generators

- 6.2.1 Description

- 6.2.2 Main Features

- 6.2.3 Block Diagram

- 6.2.4 Pin Diagram

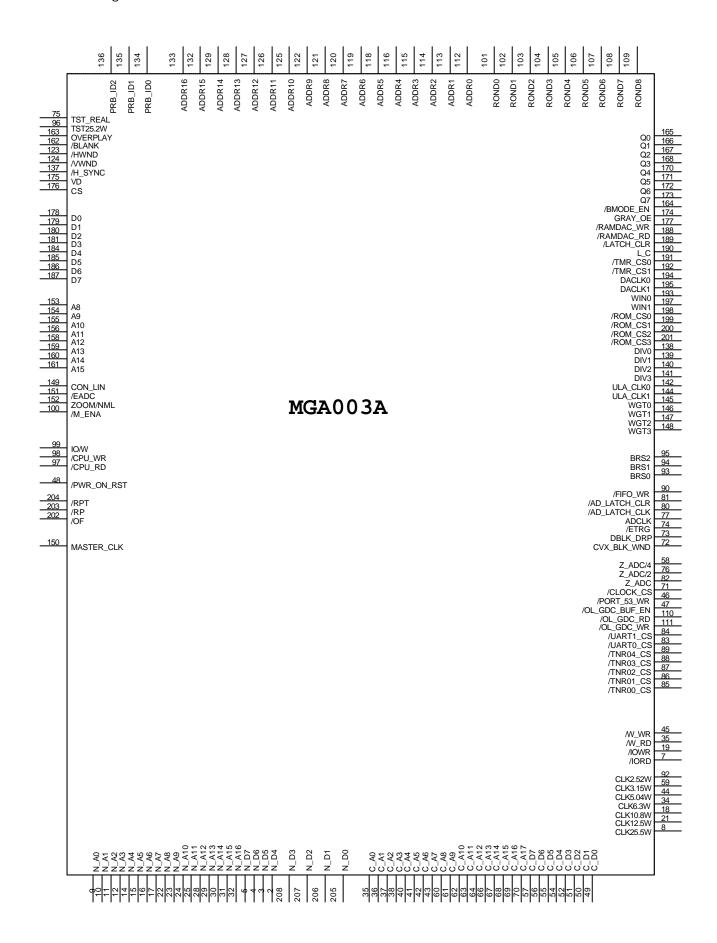

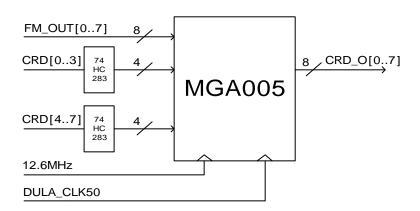

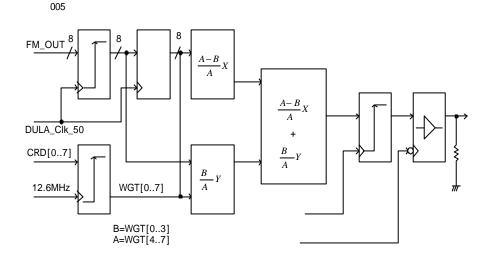

- 6.3 MAGA005 Manual

- 6.3.1 Description

- 6.3.2 Block Diagram

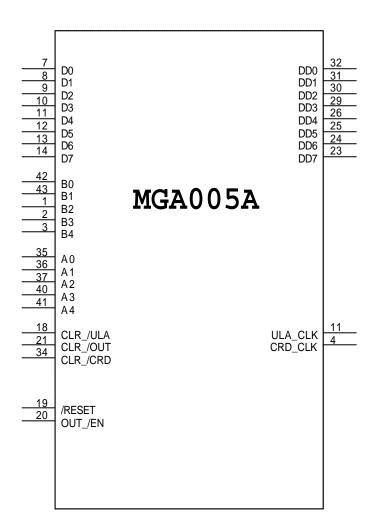

- 6.3.3 Pin Diagram

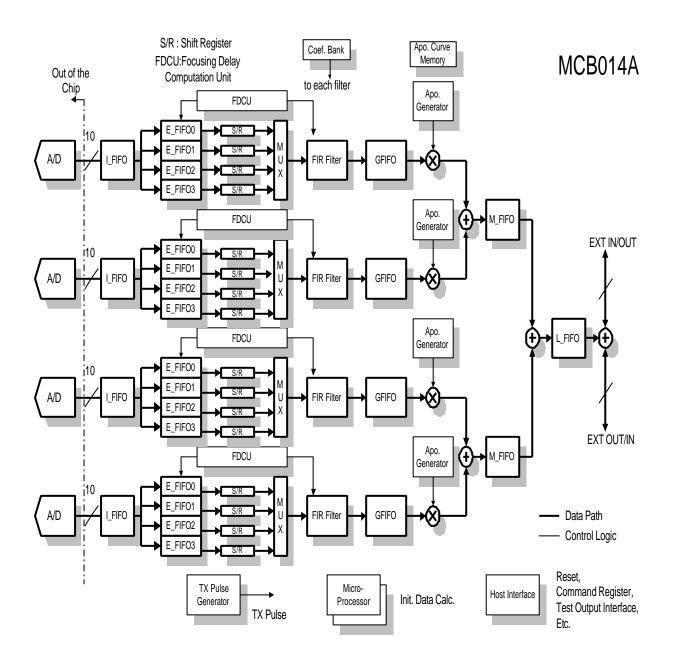

- 6.4 MCB014 Manual

- 6.4.1 Main Features

- 6.4.2 Block Diagram

- 6.4.3 Pin Diagram

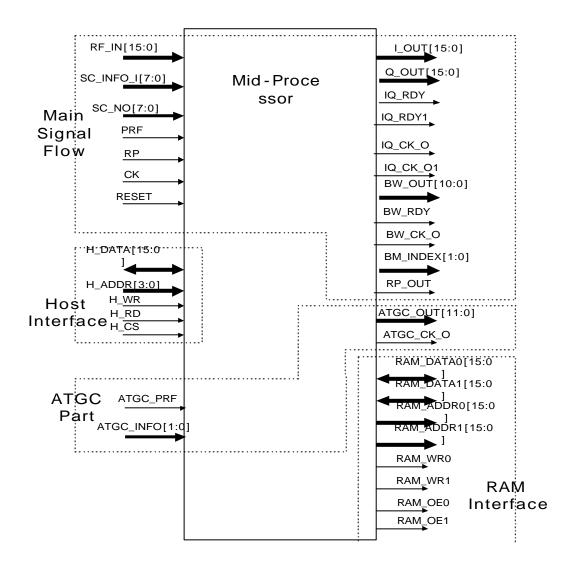

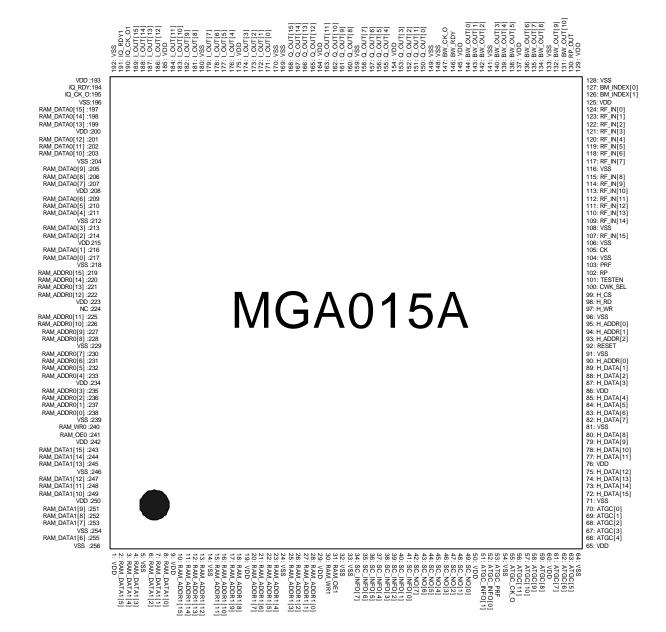

- 6.5 MGA015A Manual

- 6.5.1 Main Features

- 6.5.2 Block Diagram

- 6.5.3 I/O Signal Overview

- 6.5.4 PIN Diagram

# 7. I/O Map

# A TABLE OF CONTENTS

# **Section 3. Sub Apparatus**

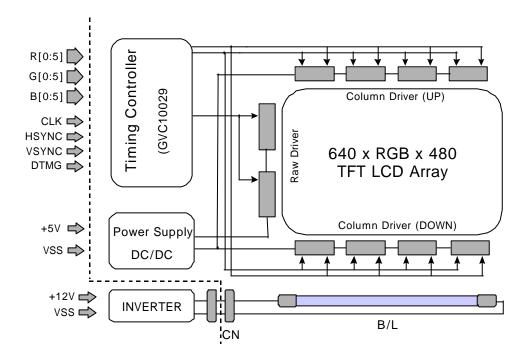

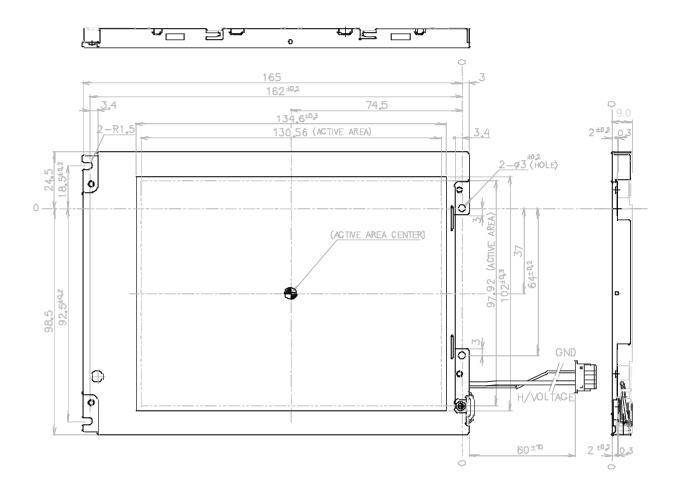

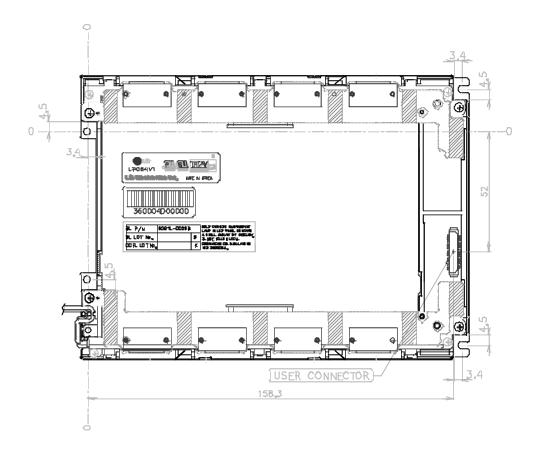

#### 1.LCD

- 1.1 General Description

- 1.1.1 General Display Characteristics

- 1.2 Maximum Ratings

- 1.3 Electrical Specifications

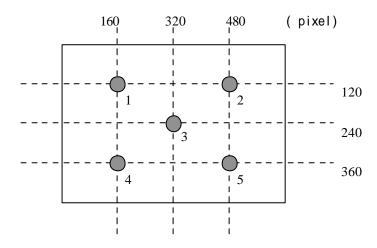

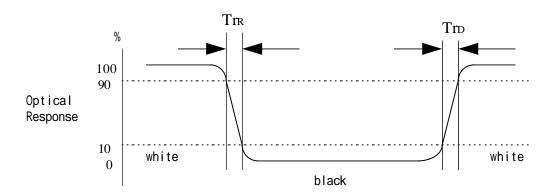

- 1.4 Optical Specifications

- 1.5 Interface Connections

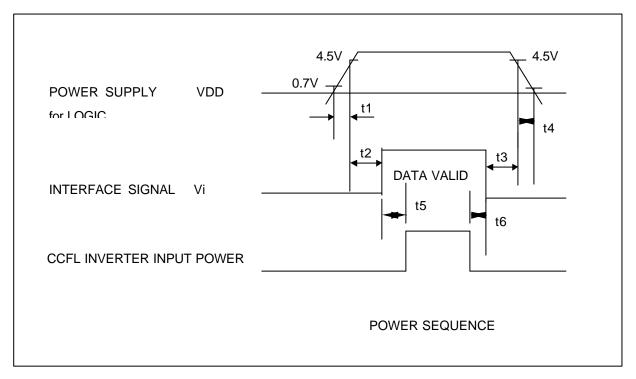

- 1.6 Power Sequence

- 1.7 Mechanical Characteristics

- 1.8 International Standards (TBD)

- 1.8.1. Safety

- 1.8.2. EMC

- 1.9 Handling Precautions

- 1.9.1.Mounting Precaution

- 1.9.2. Operation Precaution

- 1.9.3 Electrostatic Discharge Control

- 1.9.4 Precaution For Strong Light Exposure

- 1.9.5 Storage

- 1.9.6 Handling precautions For Protection Film

- 1.9.7 Safety

- A 1 Brightness

- A 2 Response Time

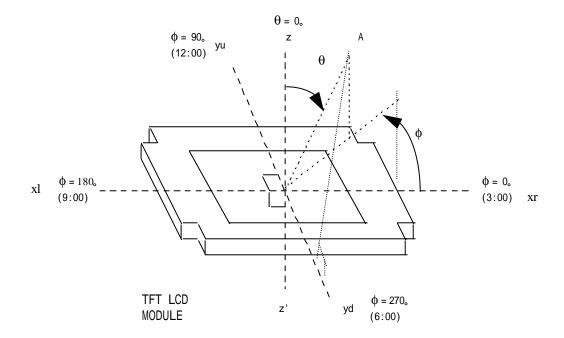

- A 3 Viewing angle

#### 2. Adapter

- 2.1 Spec. and Range of application

- 2.2 Block Diagram

- 2.3 Schematic Diagram

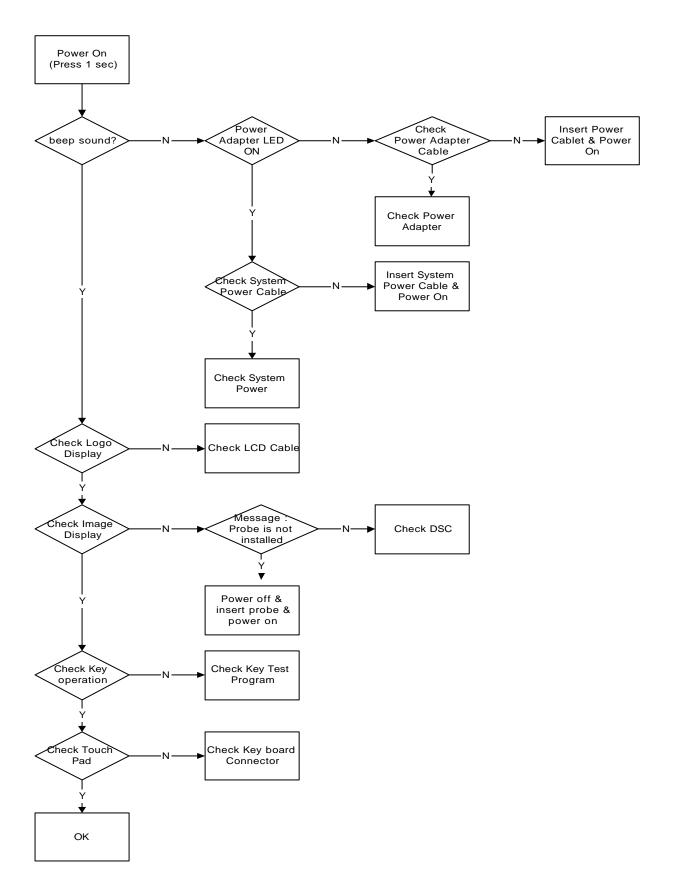

# Section 4. Trouble Shooting

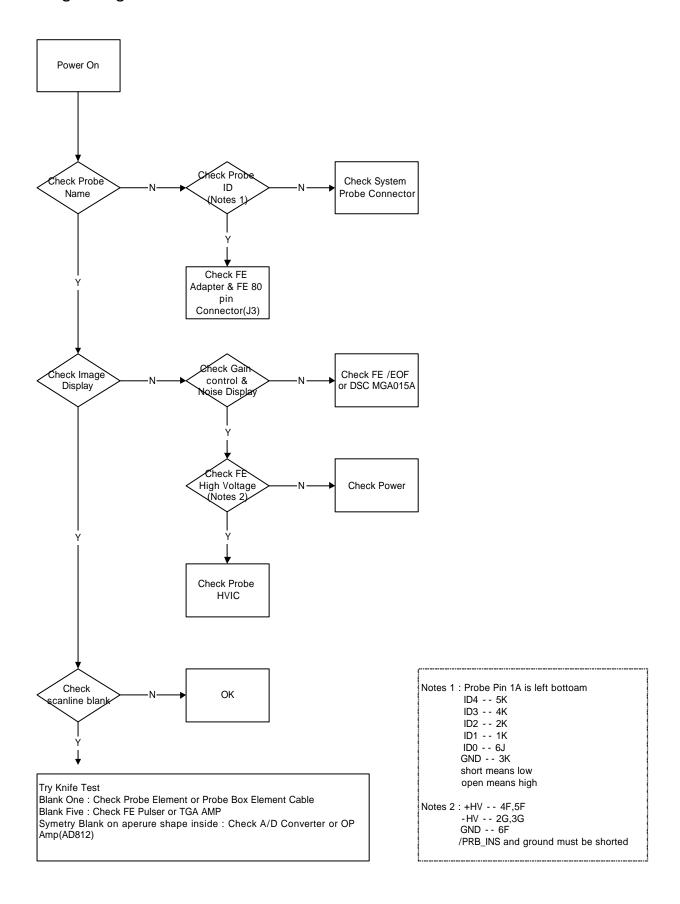

#### 1. Trouble shooting

- 1.1 System Booting Diagnosis.

- 1.2 Image1 Diagnosis

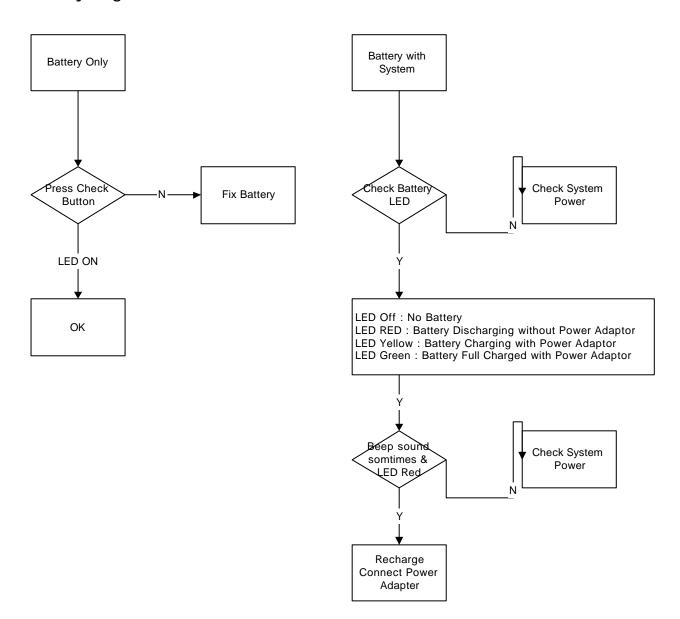

- 1.3 Battery Diagnosis

- 1.4 Etcetera Diagnosis

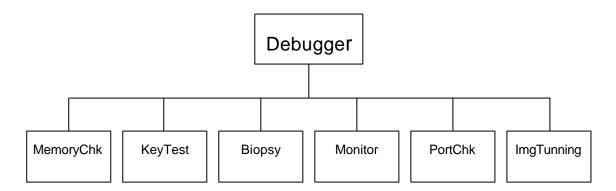

# 2. Debug Mode

2.1 Debug Menu

# A TABLE OF CONTENTS

# Section 4. Trouble Shooting

- 2.2 Image Memory Debugger Menu

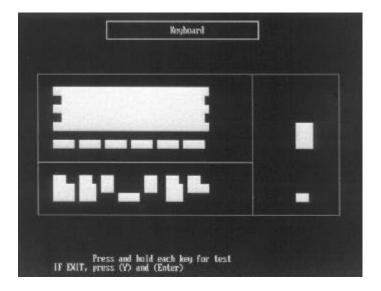

- 2.3 Keyboard Menu

- 2.4 Biopsy Menu

- 2.5 Monitor Menu

- 2.6 8085 I/O Debugger Menu

# Section 5. Replacement Procedures

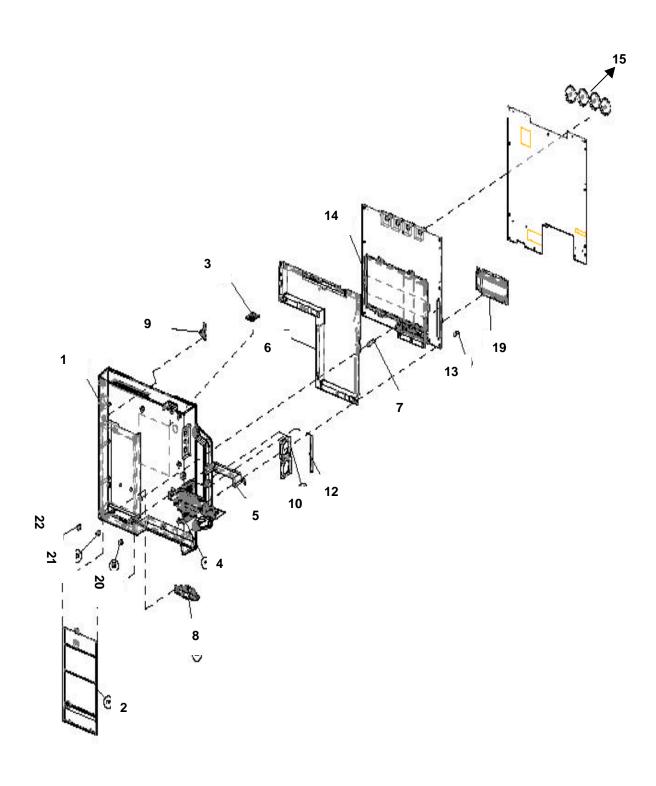

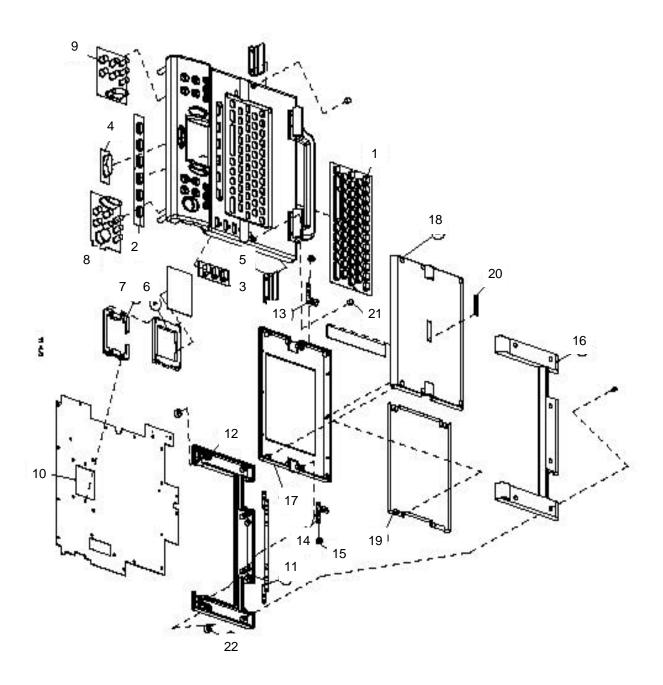

# 1. Spare Parts Assembling Diagram

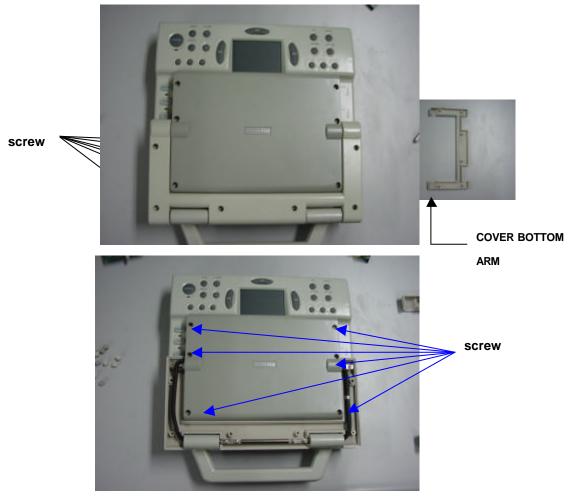

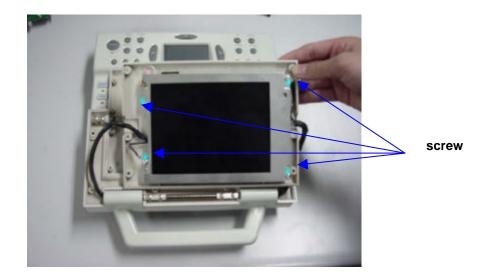

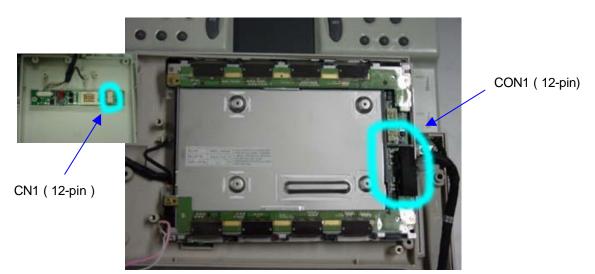

- 1.1 TFT LCD Monitor Replacement Method

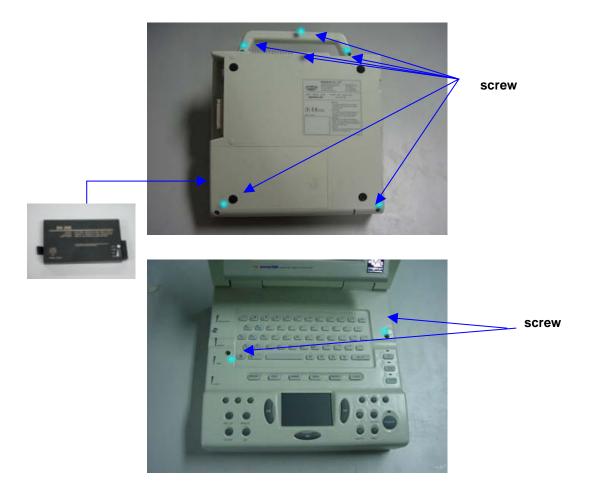

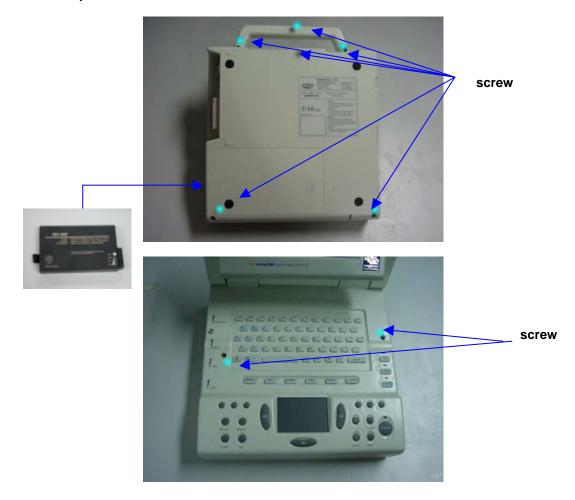

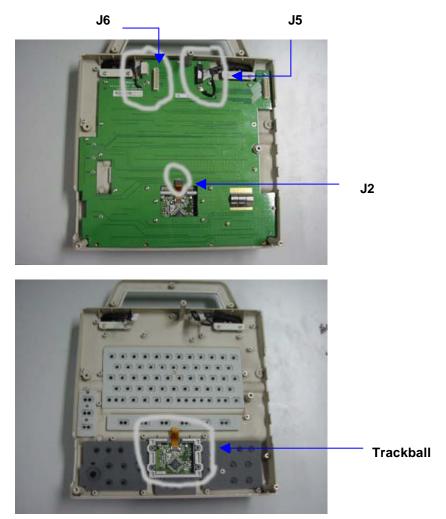

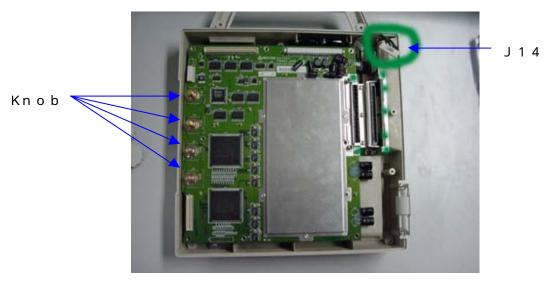

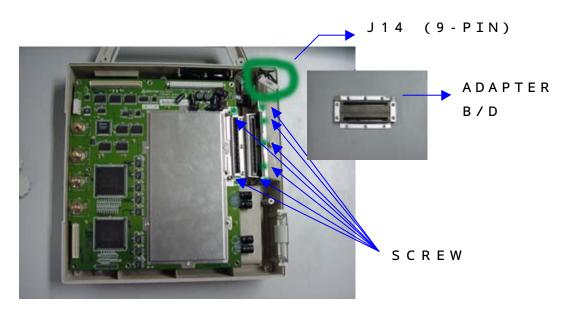

- 1.2 KEY Matrix PCB Replacement Method

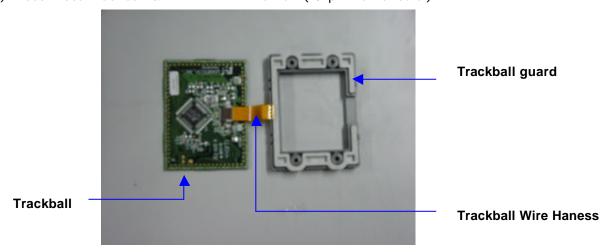

- 1.3 Trackball Replacement Method

- 1.4 Each PCB Board Replacement

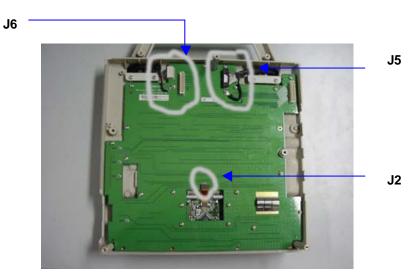

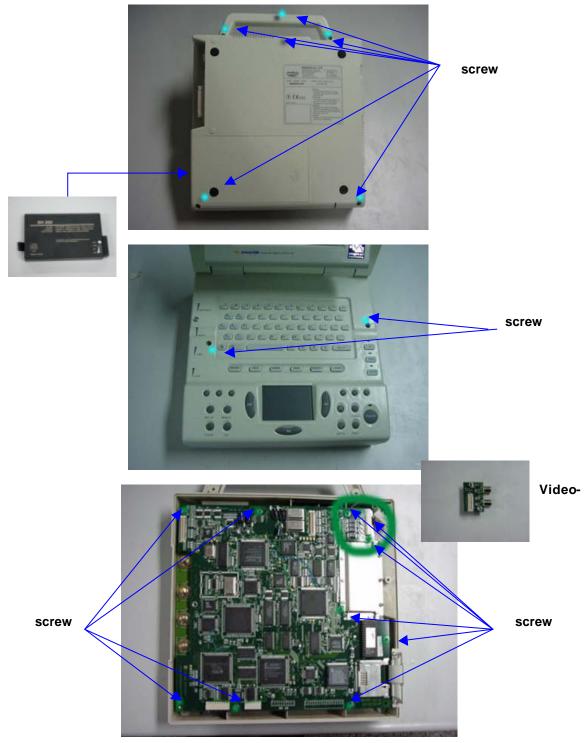

- 1.4.1 DSC Board Replacement Method

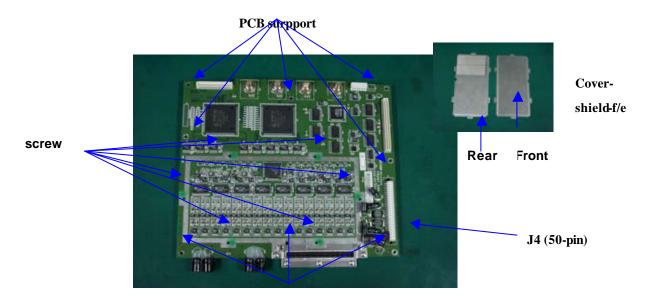

- 1.4.2 Front End Board Replacement Method

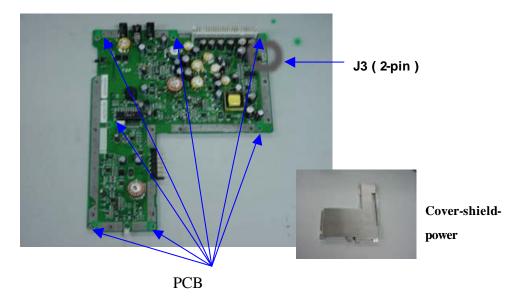

- 1.4.3 Power Board Replacement Method

#### 2.Parts List

- 2.1 Cover Body Bottom Assy Exp.

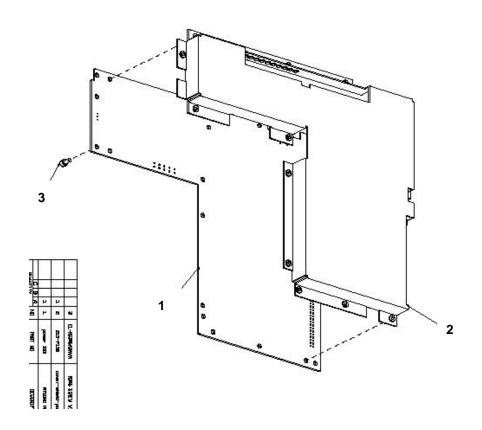

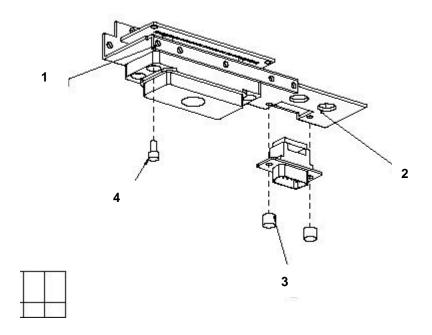

- 2.2 Power Assy Exp.

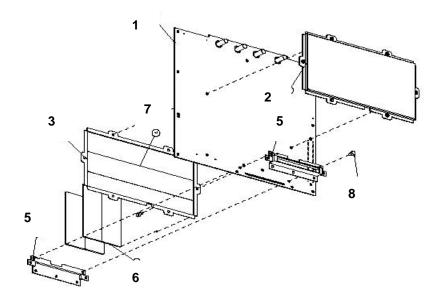

- 2.3 AY\_FE\_Board\_Exp.

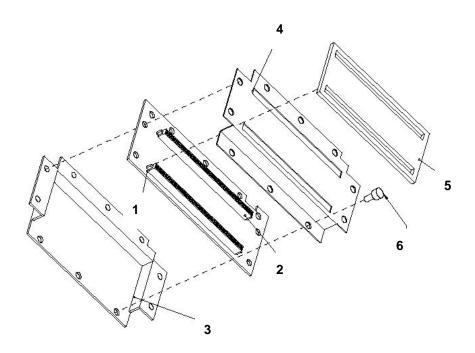

- 2.4 Adapter B/D Exp.

- 2.5 Cover Assy Body Top Mysono Exp

- 2.6 SPC Board Assy Exp.

# Section 6. Additional Information

#### 1.Specification

- 1.1 Technical Specification

- 1.2 Safety Standard

- 1.3 Range of measurement and accuracy

- 1.3.1 B mode Range and accuracy

- 1.3.2 M mode Range and Accuracy

#### 2. Mysono 201 Compatibility Matrix

Mysono 201 Section 1.1

# 1. What is Mysono201?

Mysono201 manufactured by Medison Co.,Ltd is the newest subminiature and portable ultrasound system with high resolution, deep transmission and variable function for measurement.

- The several probes such as Curved probe, Linear probe are available for wide usage.

Mysono201 can be used in a variety of applications Abdomen, Obstetrics, Gynecology,

Vascular, Extremity, Pediatric, Cardiac, Urology.

- Mysono201 offers to excellent image quality, several measurement functions such as a standards distance, area, girth, volume by application for Obstetrics, Cardiac, etc.

# 2. System constitution

The system consists of main body, monitor, probe, accessory, etc.

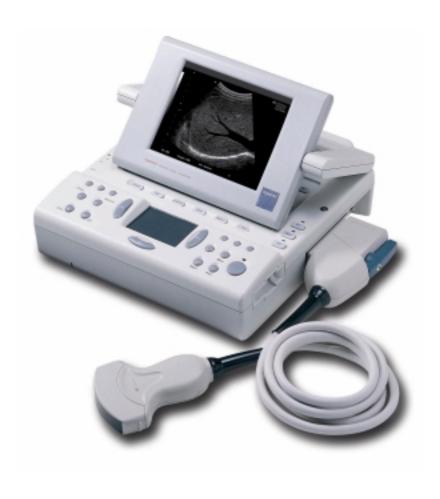

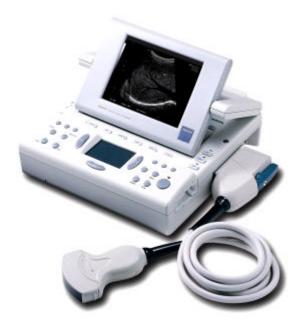

[Figure 1.1 Mysono201]

MEDISON or local distributor will make available on request circuit diagrams, components part list, descriptions, calibration instructions or other information which assist your appropriately qualified technical personnel to repair those parts of equipment which are designed by Medison as repairable

#### 2.1 Main body

The system is classified by inside for making ultrasound image and by outside for connection to other parts. The housing of system has controllers, probe connector, connector for monitor or other accessories, handle and power switch.

# 2.2 Monitor

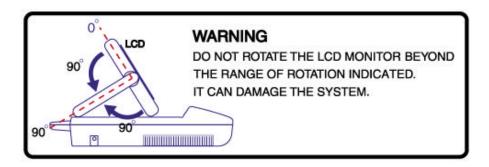

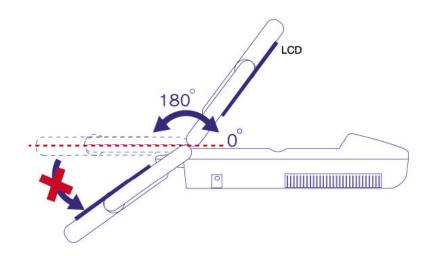

It is TFT LCD Monitor and displays ultrasound image and related information.

It connects to the main body lack of which can control the angle and the height.

[Figure 1.2 LCD Warning]

[Figure 1.3 LCD Warning]

#### 2.3 Probe

Probe generates ultrasound beam and gain the data for display the image.

Probe list and BIOPSY kit available Mysono201 is as follows;

| ID | Probe     | Biopsy kit | Application                                         |

|----|-----------|------------|-----------------------------------------------------|

|    |           |            | Mysono201(Human)                                    |

| 12 | L4-7CD    | BPL-50/65  | Small parts(Breast / Thyroid / Testicle), Muscular, |

| 12 | L4 7CD    |            | Skeletal, pediatric, Peripheral-vascular            |

| 13 | L5-9CD    | BPL-75     | Small parts(Breast / Thyroid / Testicle), Muscular, |

|    |           |            | Skeletal, pediatric, Peripheral-vascular            |

| 14 | L5-9/60CD | BPL-50/65  | Small parts(Breast / Thyroid / Testicle), Muscular, |

| 1  | 25 5/0005 |            | Skeletal I, pediatric, Peripheral-vascular          |

| 00 | C2-5/60BD | Reserved   | Abdomen, Obstetrics, Gynecology, Fetal heart        |

| 03 | C4-7BD    | BPC-50     | Abdomen, Obstetrics, Gynecology, Fetal heart,       |

|    | C4 755    |            | Pediatric                                           |

|    | EC4-      | BPC-65-E/C | Obstetrics, Gynecology, Urology                     |

| 04 | 9/13CD    |            |                                                     |

|    | Vaginal   |            |                                                     |

Human: Image setting, Safety, EMC, AP&I, QA - Total 6 Probe Release.

# 2.4 Parts

There are supplied with main body.

Coupling gel

Power code

Power adapter

Battery (Option)

**RCA Jack**

Video output cable

Portable Case

Operation manual (User guide)

Smart media (Option) - available hereafter

# 2.5 Accessories (Option)

It is the optional accessories to connect to the main system. Please refer to supplement OB of user guide.

B/W Printer

VCR

Non-Interlaced B / W Monitor

VGA Monitor

VHS Monitor

**HMD**

# 3. Safety Precautions

[Notes to users]

Thank you for purchasing the Mysono201 Ultrasound system.

To ensure safe operation and long terms performance stability, it is essential that you fully understand the functions, operating and maintenance instructions by reading this manual before operating your equipment. The system must be operated only by, or under supervision of a qualified person.

"Warning" is used to indicate the presence of a hazard that can cause severe personal injury, death, or substantial property damage if the warning is ignored.

"Caution" is used to indicate the presence of a hazard that will or can cause minor personal injury or property damage if the warnings ignored.

"Note" is used to notify the user of installation, operation, or maintenance information that is important but not hazard related. Hazard warnings should never be included under the Note signal word.

#### 3.1 Safety Precautions

- Classification:

- Class I equipment with Type BF applied parts

- Ordinary Equipment

- Non-AP/APG

- Electromechanical safety standards met:

- \_ CSA C22.2 No.601.1, Canadian Standards Association, Medical Electrical Equipment

- EN60601-1, Second Edition, including Amendments 1 and 2, European Norm, Medical Electrical

#### Equipment

- EN60601-1-2, First Edition, European Norm, Collateral Standard, Electromagnetic Compatibility

- IEC61157: 1992, International Electro technical Commission, Requirements for the declaration of the acoustic output of medical diagnostic ultrasonic equipment

- UL 2601-1, Underwriters Laboratories, Medical Electrical Equipment

#### 3.2 Electrical Safety Precaution

It is classified Class I equipment with Type BF applied parts

To ensure user safety, check the following.

Never open the system safety cover.;

There is a dangerous voltage in system inside. If any repairing or exchanging of parts is desired, ask to the authorized dealer for the service.

Do not place the system near of flammable gas or anesthesia gas. It has a danger of explosion.

Before using the system, check the housing and the cables. If it has any crack on the housing or wear away on cable, stop to use.

Whenever cleaning the system, take off the power code and the battery to avoid the danger of an electric shock.

#### WARNING

To avoid the danger of an electric shock, use the standard device for digital interface of which achieved IEC certificate. (I.e. IEC60950/EN60950 for the data processing device, IEC60601-1/EN60601-1 for medical device.)

For the more, all parts of system meet standard requirement of IEC60601-1-1/EN60601-1-1.

Check whether the peripheral device of input or output port meet standard requirement of IEC60601-1-1/EN60601-1-1 when add it.

Do not connect to the system signal in/outlet and the patient at the same time.

It is for preventing to leakage current caused by over the maximum permissible range.

Even though the system passed the test of EMI/EMC standard, it could be down the image quality or could damage the system under using magnetic filed.

If you have a poor image or image problem, check whether the source of electromagnetic waves is near of the system or not such as Mobile phone, Pager, Radio, TV or Microwave machine. Please move them far from the system or move the system from affected zone of electromagnetic waves.

Electrostatic discharge (ESD) is a shock occurred by Static electricity and a phenomenon in nature. ESD occurs in dry condition such like under using heater or air conditioner.

The static electricity occurred by a user or a patient can affect to the system or the probe sometimes. To prevent this problem, please be well aware as follow.

- : Spray the prevent of static electricity spray to carpet or Linoleum

- Use met for protection of static electricity

- Connect a ground between the system and table or bad for patient

CAUTION

#### 3.2.1 System care

Check the following.

In case that tie too much or twist the probe connected with patient, system could be wrong work.

Wrong cleaning or sterilization of the parts connected with patient is dangerous.

Refer to "3.4 Maintenance & Cleaning" in this manual.

Do not soak the cable in liquid. It cannot prevent flood.

Do not use strong solvents such as thinner or benzene, or abrasive cleansers.

**CAUTION**

Since these will damage the cabinet.

In general, only treat with waterproof on the ultrasound lens part (Safety grade: IPX7). Do not soak the probe in liquid except the special case with cleaning guide.

Do not turn the system off under store the image. That will damage the memory inside.

Turn the system off when remove the probe form the system or connect it to the system.

Do not keep the system over one hour with close LCD monitor under the system is working. That will damage the keyboard.

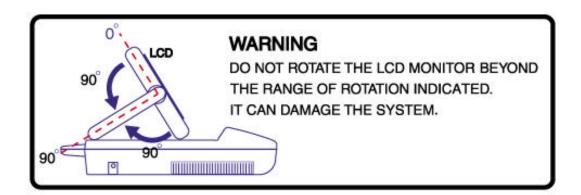

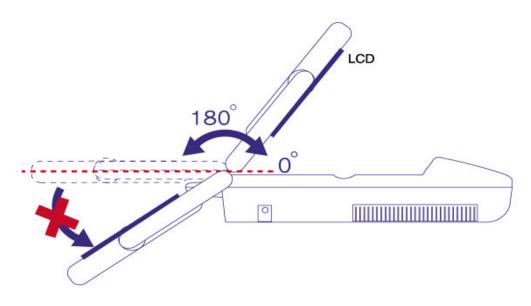

WARNIN G The turning radius is limited to suitable use. If it is over the limitation, that will damage LCD monitor.

[Safety Figure 1. Warning for LCD angle]

[Safety Figure 2. Warning for LCD angle]

# 3.2.2 Battery

Keep in mind the warning and caution to prevent explosion, heat or smoke generation in battery.,

|         | Do not disassemble or modify the battery.                                 |

|---------|---------------------------------------------------------------------------|

|         | Keep the circumstance temperature condition when using the battery.       |

|         | - Charge: 0 <sup>0</sup> ~ 45 <sup>0</sup> C                              |

|         | - Discharge: -10 <sup>0</sup> ~ 60 <sup>0</sup> C                         |

|         | Do not short between terminals of battery.                                |

| WARNING | Do not use the battery under the circumstance like as fire, moisture.     |

|         | Do not charge the battery where is near of fire or heater.                |

|         | Keep out of the sun when keep the battery.                                |

|         | Keep out the sharp material to face with battery and do not deliver the   |

|         | shock directly to it.                                                     |

|         | Take away the battery from the system when do not use it for a long time. |

|         | Do not use the battery except supplied by Medison                                     |

|---------|---------------------------------------------------------------------------------------|

|         | Do not use a battery except made by Medison.                                          |

|         | Do not charge a battery with non- allowed method.                                     |

|         | (Don't use other charge method)                                                       |

|         | Keep a battery from moisture.                                                         |

| CAUTION | If smell or burn under using battery, discontinue use of system prompt,               |

|         | remove a battery.                                                                     |

|         | Keep the battery under the circumstance temperature -20 $^{\circ}$ ~ 50 $^{\circ}$ C. |

|         | System working condition and a number of charge/discharge times of                    |

|         | battery affect to time of charge/discharge.                                           |

|         | Medison guaranty the battery during 6 month (battery capacity 50%).                   |

# 3.2.3 Safety Symbols

The international Electrotechnic Commission (IEC) has established a set of symbols for medical electronic equipment that classify a connection or warm of any potential hazards. The classifications and symbols are shown below.

Isolated patient connection (IEC 601-1-Type BF)

Power Switch represent ON and OFF, respectively.

This symbol identifies a safety note. Ensure you understand the function of this control before using it. Control function is described in the appreciate operation manual.

Output port or Parallel port of VGA

Output port of VHS

Non-interlaced B/W Printer port

Printer remote output port

**Humidity protect**

#### 3.3 Physical Safety Precaution

If you have experienced any trouble with the equipment, switch it off immediately, and contact to Service center or its authorized dealer for assistance.

Do not use the system under working wrong or trouble.

Non-continuous scanning is caused by hardware problem. It must be repaired.

The using of Ultrasound always needs a careful attention.

Under the principles of ALARA, energy delivered should be "as low as reasonably achievable" to perform study.

Read the explanation about biopsy before using it. Refer to user explanation parts of probe an appendix.

Certify biopsy Needle before using it. Do not use curved needle.

#### ALARA TRAINING PROGRAM

WARNING

Ultrasound is considered safe at low clinical levels. At high levels and longer exposures, however, its safety is not completely understood. For this reason, always exercise caution when exposing patients to ultrasound. Always use the lowest transmit power levels.

And minimize time of exposure. Under the principles of ALARA, energy delivered should be "as low as reasonable achievable" to perform your study.

The following is a public statement by the one of United Stated Ultrasound Association, AIUM, on the safety of ultrasound diagnosis.

Ultrasound has been in use since the 1950's. AIUM declares the clinical safety of ultrasound scanning and acknowledges its effectiveness as the type medical equipment and its possible use for diagnosis of pregnant women.

There has been no case which shows cause of any physical damage to either patient or user during properly performed diagnosis with an ultrasound scanner. Although it might be possible that unknown effects of ultrasound may come to light in the future, so far the benefits far outweigh any unproved danger. Theoretically, there are two possible ways that ultrasound could have negative affect on the human body.

One is the heat generated by ultrasound as it passes through the human body. Doppler produces the most heat, and it followed by color and B-mode imaging. However, even in the case of Doppler the amount of heat is so minor that there is no equipment that can measure it. The other one is the possible formation of a cavity by the ultrasound. However, there has been no clear evidence that this can actually occur in the human body.

In conclusion, no negative biological effects of ultrasound have been proven thus far.

#### 3.4 Maintenance and cleaning

WARNING WARNING the plug from the power supply. (Remove the battery from the system, too)

#### 3.4.1 Probe

WARNING

Always use protective eyewear and gloves when cleaning and disinfecting probes and Biopsy guide adapter.

CAUTION

Probes must be cleaned after each use. Cleaning the probe is an essential step prior to effective disinfection or sterilization. Be sure to follow the manufacturer's instructions when using disinfectants.

Do not allow sharp objects, such as scalpels or cauterizing knives, to touch probes or cables.

When handling a probe, do not bump the probe on hard surfaces.

Probe is very important part to judge the image quality. The optimum image can display under using the correct probe.

#### 3.4.1.1 Cleaning

CAUTION

Do not use lacquer thinner ethylene oxide or any other organic solutions, as these can destroy the membrane of the probe.

Do not use a surgeon's brush when cleaning probes. The use of even soft brushes can damage the probe.

During cleaning, disinfection, and sterilization, orient the parts of the probe that must remain dry higher than the wetted parts until all parts are dry. This will help keep liquid from entering non-liquid-tight areas of the probe.

- 1) Disconnect the probe from the system.

- 2) Remove any sheaths, biopsy guide adapters, or biopsy needle guides (biopsy guide adapters are re-usable portion of the biopsy guide and can be sterilized.)

- 3) Discard sheaths (sheaths are single-use item)

- 4) Use a soft cloth lightly dampened in a mild soap or compatible cleaning solution to remove any particulate matter or body fluids that remain on the probe or cable.

- 5) To remove remaining particulates, rinse with water up to the immersion point.

- 6) Wipe with a dry cloth; or wipe with a water-dampened cloth to remove soap residue, and then wipe with a dry cloth.

#### 3.4.1.2 Sterilization

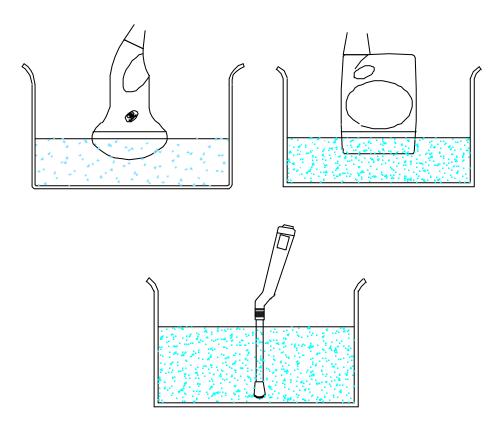

Apply this sterilization way to EC4-9/13CD probe only.

A 10<sup>-6</sup> reduction in pathogens should be reached following the sterilization procedures in this manual and using the following MEDISON recommended solutions. The following disinfectants are recommended because of both its biological effectiveness (as qualified through the FDA 510(k) process) and its chemical compatibility with MEDISON ultrasound product materials.

| Solution | Country | Туре   | Active ingredient | FDA 510(k) |

|----------|---------|--------|-------------------|------------|

| Cidex    | USA     | Liquid | Gluteraldehyde    | K934434    |

WARNING

If a pre-mixed solution is used, be sure to observe the solution expiration date. The level of disinfection required for a device is dictated by the type of tissue it will contact during use. Ensure that the solution strength and duration of contact are appropriate for disinfection or sterilization. Be sure to follow the manufacturer's instructions.

In neurosurgical application, sterilized probes should be used with a pyrogen-free sheath.

CAUTION

Using a non-recommended disinfection solution, incorrect solution strength, or immersing a probe deeper or for a period longer than recommended can damage or discolor the probe and will void the probe warranty.

Do not immerse probes longer than one hour, unless they are sterilizable. Probes may be damaged by longer immersion times.

Sterilize probes using only liquid solutions. Using autoclave, gas(EtO), or other non-MEDISON-approved methods will damage your probe and void your warranty.

- 7) Mix the disinfection solution (or sterilization solution, for sterilizable probe) compatible with your probe according to label instructions for solution strength. A disinfectant qualified by the FDA 510(k) process is recommended.

- 8) Immerse the probe into the disinfection solution (or sterilization solution, for sterilizable probe) as shown in the figures below for your probe.

- 9) Follow the instructions on the disinfection (or sterilization, for sterilizable probe) label for the duration of probe immersion. Do not immerse probes longer than one hour, unless they are sterilizable.

- 10) Using the instructions on the disinfectant or sterilization label, rinse the probe up to the point of immersion, and then air dry or towel dry with a clean cloth (or a sterile cloth, for sterilizable probe).

- 11) Examine the probe for damage such as cracks, splitting, fluid leaks, or sharp edges or projections. If damage is evident, discontinue use of the probe and contact your customer service representative.

#### 3.4.2 Biopsy guide adaptor and Needle guide

The reusable external surface of biopsy guide adaptor can sterilize under the condition as below. It is possible to reduce the pathogens up to 10<sup>-6</sup> as following process.

WARNING Gloves and safety mask should be worn during cleaning and sterilizing the probe and biopsy guide adapters.

Biopsy guide have to clean after using. It is very important process.

When using the disinfecting solution, follow the user guide published by manufacturer.

Keep out of the sharp things such like a mess for a surgical operation.

Be careful to avoid striking the biopsy guide with hard material.

# 3.4.2.1 Cleaning of the stainless biopsy guide

- 1) Take off the biopsy guide assembly parts from the probe after using.

- 2) Disassemble the biopsy guide parts each one.

- 3) Remove an alien substance still remained on each part using by small brush and water.

- 4) Rinse it with water to remove again an alien substance.

#### 3.4.2.2 Sterilizing of the stainless biopsy guide

Sterilize it by using an autoclave or Ethylene Oxide.

- 1) Complete the following process after sterilization.

- 2) Check the biopsy guide adaptor whether it has a crack, division, or any other damage on it. If there is some damage, stop to use and contact to Medison service agency or its authorized local service agency.

# 3.4.2.3 Cleaning of plastic biopsy guide

Take off the biopsy guide assembly parts from the probe after using.

- 1) Disassemble the biopsy guide parts each one. The consumable parts cannot sterilize.

- 2) Remove an alien substance still remained on reusable part using by small brush and water.

- 3) Rinse it with water to remove again an alien substance.

# 3.4.2.4 Sterilizing of plastic biopsy guide

Sterilize only a chemical pasteurization at a low temperature.

CAUTION

It can get the permanent damage by sterilization using autoclave, gas or radioactivity.

4) Sterilize it by using a chemical pasteurization at a low temperature approved by FDA 510(K). Check the time (normal 10 hours) and the temperature of solution.

It is a biologically, chemically suitable disinfecting solution approved by FDA 510(k) in U.S.A.

| Solution   | Country | Туре   | Active ingredient | FDA 510(k) |

|------------|---------|--------|-------------------|------------|

| Cidex      | USA     | Liquid | Gluteraldehyde    | K934434    |

| Cidex Plus | USA     | Liquid | Gluteraldehyde    | K923744    |

- 5) Complete the following process after sterilization.

- 6) Check the biopsy guide adaptor whether it has a crack, division, or any other damage on it. If there is some damage, stop to use and contact to Medison service agency or its authorized local service agency.

#### 3.4.3 Surface of system

Follow as below..

WARNING

Gloves and safety mask should be worn during cleaning and sterilizing the surface of system.

CAUTION

Use only the solution recommended by Medison.

# 3.4.3.1 Cleaning

- 1) Turn the system off and then remove the plug from the power source.

- 2) Use a soft cloth lightly moistened with a mild soap or detergent solution to clean the system surface.

#### 3.4.3.2 Sterilization

- 3) Use a disinfecting solution with suitable concentration recommended by user guide. Medison recommend the solution approved by FDA 510(k) in U.S.A.

- 4) Check the using time and the concentration of the solution as following the caution on the label.

- 5) Dry it with a soft sterile cloth.

Mysono 201 Section 1-4. Installation

# 4. Installation of Mysono201

# 4.1 Connecting and removing the probe

The system has only one probe connector.

- How to connect the probe

- 1) Connect the probe to the probe connector located at the right side of the system.

- 2) Turn the locking lever on the probe connector clockwise to fix the probe.

- How to remove the probe

- 1) Turn the locking lever on the probe connector counter-clockwise to remove the probe.

- 2) Take off the probe from the system.

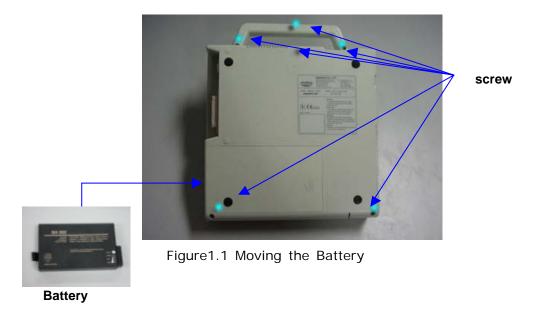

#### 4.2 Connecting and removing the battery

It is optional part to supply the battery.

- How to connect the battery

- Remove the cover of battery connector located at the bottom of system by pushing forward outside.

- 2) Insert the battery to the battery connector by matching the bottom of the battery and the system. After fixing the location of the connector pin between the battery and system, press it softly until complete the connection.

- 3) After complete connection, close the cover of battery connector of the system.

- How to remove the battery

- 1) Turn off the system power.

- 2) Remove the cover of battery connector located at the bottom of system by pressing forward outside.

- Take hold of the battery handle and lift it slightly. Then push it forward outside of the system.

- 4) After remove the battery, close the cover of the system battery connector.

#### 4.3 Charge and discharge of the battery

The battery has to charge before using.

- How to charge the battery

- 1) Insert the battery as how to connect the battery

- 2) Connect the system and AC adaptor supplied with the system. Refer to [appendix 0b. connecting the peripheral device] in user manual.

- 3) The battery is charging during AC adaptor connecting.It is possible to charge under the state both the system on and off.

Mysono 201 Section 1-4. Installation

In case of the system on, it takes about 5 hours to charge.

In case of the system off, it takes about 3 hours to charge.

If need a more information of the time for charge or discharge, refer to [Appendix C. System specification] in the user manual.

Check the battery state by LED color on the system during charging.

Without Battery: No ColorUnder charging: OrangeComplete charging: Yellow

- Take off the adaptor: Red

#### Discharge the battery

When the battery is discharged (the system is working without AC adaptor), the system power will be compulsorily turned off after a period of time (90 minutes) for safety and efficiency of battery and user will hear the warning "beep" sound every 10 seconds.

#### 4.4 Power ON / OFF

Hold the pressing the power switch located at the left side of the system for minimum 1sec. whenever turns on/off the system. It is to prevent the system down and battery discharge.

- How to turn on the system

- Hold the pressing the power switch for minimum 1sec. with connecting the AC adaptor or inserting the charged battery.

- 2) Check the image display on the monitor.

- How to turn off the system

- 1) Hold the pressing the power switch for minimum 1sec.

- 2) Check the image disappears on the monitor and switch off.

#### 4.5 Using AC adaptor

It takes about 5 hours to charge completely under connection of AC adaptor to the system. Refer to [Appendix Ob. connecting the peripheral device] in user manual. Mysono 201 Section 1-5. Function

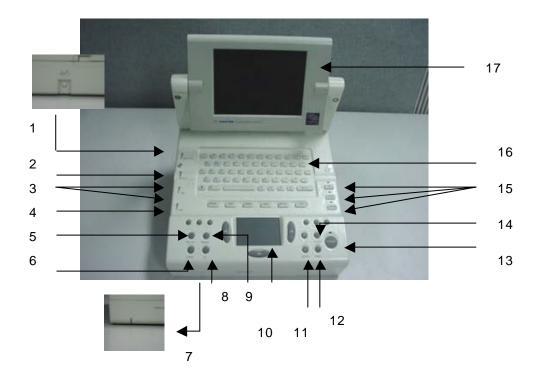

# 5.Mysono201 Function

| No. | CONTROLS     | DESCRIPTION                                           |  |

|-----|--------------|-------------------------------------------------------|--|

| 1   | Power switch | Turns power on / off → about 1 sec.                   |  |

|     |              | Control the Brightness of LCD monitor.                |  |

| 2   | Brightness   | Turn it to clockwise for brightness                   |  |

|     |              | Turn it to counter-clockwise for darkness             |  |

|     |              | Use either Near dial or Far dial                      |  |

| 3   | Near / Far   | When control the Near gain, use Near dial             |  |

|     |              | When control the Far gain, use Far dial               |  |

|     |              | Control the image gain                                |  |

| 4   | Gain         | Turn it to clockwise for increasing the gain          |  |

|     |              | Turn it to counter-clockwise for decreasing the gain  |  |

| 5   | Set-up       | Change the mode into set-up                           |  |

| 6   | Clear        | Delete the value on the image area such as Text, Body |  |

|     | Cleal        | Marker, Indicator, measured value, etc.               |  |

|     |              | Display the status of Battery.                        |  |

|     |              | Disconnect the Battery: No Color                      |  |

| 7   | Battery LED  | Charging the battery: Orange                          |  |

|     |              | Full charge: Yellow                                   |  |

|     |              | Remove the battery adapter: Red                       |  |

| 8   | GA           | Measure GA(Gestational Age)                           |  |

Mysono 201 Section 1-5. Function

| No. | CONTROLS         | DESCRIPTION                                              |  |  |

|-----|------------------|----------------------------------------------------------|--|--|

|     | Manauma          | Mode for measuring of distance, volume, circumference,   |  |  |

| 9   | Measure          | etc.                                                     |  |  |

| 10  | Touch pad        | Touch pad                                                |  |  |

|     |                  | Control the image depth.                                 |  |  |

| 11  | Depth            | Up key for shallow depth of the image                    |  |  |

|     |                  | Down key for deep depth of the image                     |  |  |

| 12  | Printer          | Print the indicated image.                               |  |  |

|     |                  | Save the present image on the monitor.                   |  |  |

| 13  | Store            | It is possible to check the saved image by using I-View. |  |  |

|     | 3.010            | And can be back up by using smart media. (This           |  |  |

|     |                  | function will be added in the future.)                   |  |  |

|     |                  | ON/OFF the image scan.                                   |  |  |

| 14  | Freeze           | Cine function, the image saving, printing or measuring   |  |  |

| '-  | 110020           | is available under freeze.                               |  |  |

|     |                  | But the image saving is available only 2D mode.          |  |  |

|     |                  | Control knobs to select the image mode                   |  |  |

|     |                  | 2D/SYN: To 2D mode, press it one time. To Synthetic      |  |  |

|     |                  | mode, press it again under 2D mode.                      |  |  |

|     |                  | M: Change 2D/M by pressing this button.                  |  |  |

|     |                  | Display 2D image on the left side of the monitor and M   |  |  |

| 15  | 2D/SYN, M, DUAL  | mode image on the right side of the monitor.             |  |  |

|     | 25,6,11,11,25,12 | Change only M mode by pressing again this button         |  |  |

|     |                  | under 2D/M mode.                                         |  |  |

|     |                  | This button works as toggle button between 2D/M and      |  |  |

|     |                  | M mode under M mode.                                     |  |  |

|     |                  | Dual: Change Dual mode.                                  |  |  |

|     |                  | It works as alteration to left/right of activated Image. |  |  |

| 16  | Key board        | Use it when input the text or set the image.             |  |  |

| 17  | LCD monitor      | Display most of information for using such like a        |  |  |

|     | LCD IIIOHIIO     | ultrasound image, data, user menu, etc.                  |  |  |

Mysono 201 Section 1-5. Function

# Mysono201 P/M Check List

| Date:                                                     | Dis                                   | tributor:     |          |             |         |

|-----------------------------------------------------------|---------------------------------------|---------------|----------|-------------|---------|

| Hospital                                                  |                                       | System Ser    | ial      |             |         |

| Customer                                                  |                                       | S/W Versio    | n        |             |         |

| Address                                                   |                                       |               |          |             |         |

| Tel. no                                                   |                                       | Warranty      |          |             |         |

| Instructions : This information is                        | for warranty check. Please fill up    | all items.    |          |             |         |

|                                                           | Items                                 |               | Good     | Bad         | Remarks |

| I. Check the pack                                         | ing items (compare with packing I     | ist)          |          |             |         |

| II. Condition of sy                                       | stem housing                          |               |          |             |         |

| III. Probe conditio                                       | n                                     |               |          |             |         |

| A. Functional ope                                         | eration & test (system initialization | state)        |          |             |         |

| 1. System work                                            | ks well when power on.                |               |          |             |         |

| 2. Monitor TES                                            | Т                                     |               |          |             |         |

| 3. Key Board T                                            | EST                                   |               |          |             |         |

| B. Probe test (ea                                         | ch probe)                             |               |          |             |         |

| 1. Check the p                                            | robe shape                            |               |          |             |         |

| 2. Knife TEST                                             |                                       |               |          |             |         |

| C. Operational Mo                                         | ode Tests                             |               |          |             |         |

| 1. 2D Mode/SY                                             | N                                     |               |          |             |         |

| DUAL Mode                                                 |                                       |               |          |             |         |

| M Mode                                                    |                                       |               |          |             |         |

| 2. Measuremen                                             | t TEST                                |               |          |             |         |

| D . Electrical Test                                       | & Calibration                         |               |          |             |         |

| 1. Power Suppl                                            | у                                     |               |          |             |         |

| 2. System Calik                                           | oration                               |               |          |             |         |

| 3. Power Cord/                                            | Plug and 110/220 switch               |               |          |             |         |

| E. Mechanical ope                                         | eration                               |               |          |             |         |

| 1. Circuit boards, plugs, jacks, and connectors seated    |                                       |               |          |             |         |

| 3. Seating & connection of cables & cords to peripherals  |                                       |               |          |             |         |

| F. Echo printer, External monitor, Multi-form camera, VCR |                                       |               |          |             |         |

| When you finish<br>Confirmation Signa                     | filling all up, please send this shee | et to Medison | by fax o | or air mail |         |

| Service agency: Customer signature                        |                                       |               |          |             |         |

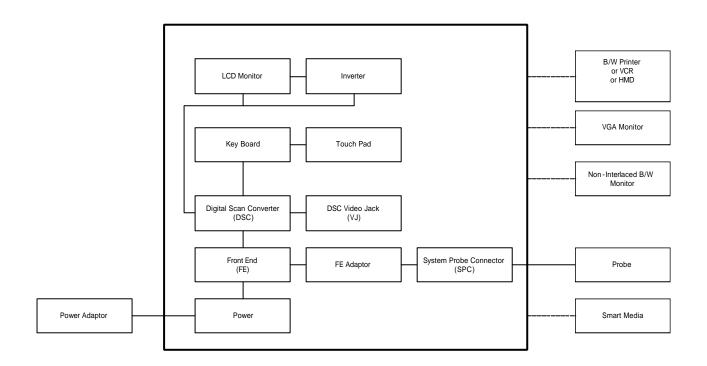

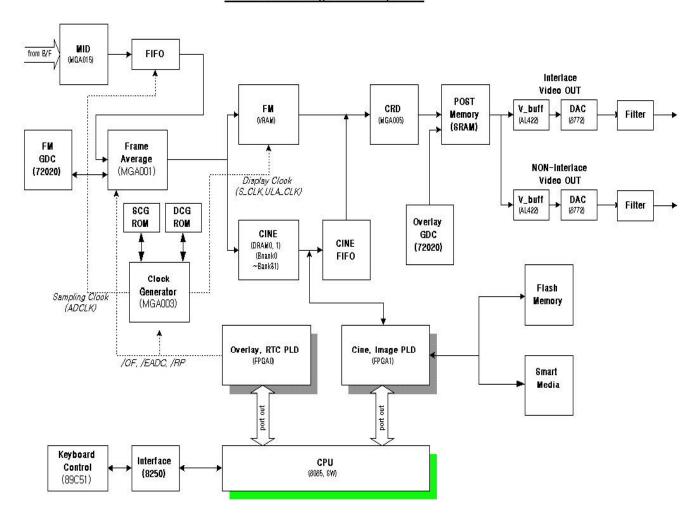

# 1. System Block Diagram

System Bolck Diagram

# 2. Front-End Board (F/E)

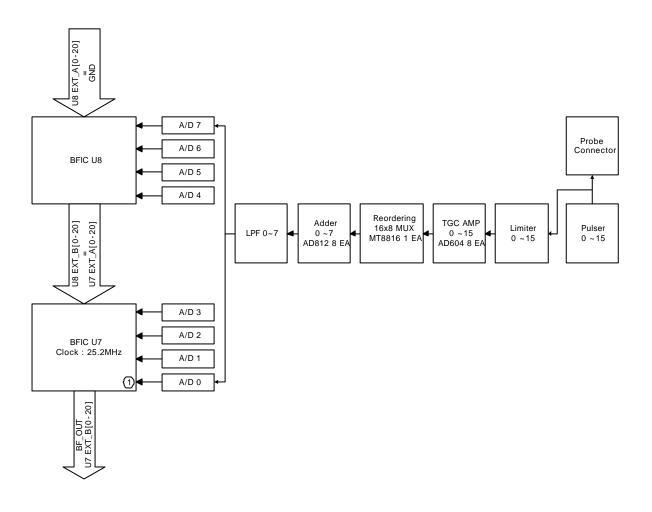

#### 2.1 General Description

F/E board receives the echo signal of ultrasound and the signal clamps the high voltage to +/-0.6 V by Limiter then pass through TGC Amp. And then it reordering and its signal path is reduced in half by OP Amp Adder that add the Symmetrical signal per scanline.

Then, to reduce the Aliasing, pass through the Low pass Filter and travels it to Beamforming IC after converting it to A/D. Beamforming IC control the signals of 8 channel by Rx focusing, and forward them to Mid Processor IC MGA015A on DSC.

Its main components are;

- MOSFET Driver EL7222 x 16 ea

- PMOS TP2520 x 16 ea

- NMOS TN2524 x 16 ea

- Dual TGC Amp AD604 x 8 ea

- Cross Point Switch (16 x 8) MT8816 x 1 ea

- OP Amp AD812 x 8 ea

- Beamforming IC MCB014A x 2 ea

- XC95144 for Control x 1 ea

# 2.2 Block Diagram

# 2.3 Signal Definition

# 2.3.1 CPLD Signal Definition

| Name         | 1/0          | Description                               |  |

|--------------|--------------|-------------------------------------------|--|

| ADDR[0-5]    | Input        | HOST Address                              |  |

| /RPT         | Input        | Rate Pulse Train                          |  |

| /P_O_RESET   | Input        | Power On Reset by RC Time Constant        |  |

| DATA[0-7]    | Input/Output | HOST Data                                 |  |

|              |              | DATA[0-15] for MCB014A(BFIC)              |  |

| /PRB_INS     | Input        | Low : Probe Inserted                      |  |

|              |              | High: Probe Not Inserted                  |  |

|              |              | If Probe is inserted, then /PRB_INS=Low   |  |

| FREEZE       | Input        | Freeze                                    |  |

|              |              | If scanning is stopped, then FREEZE=high  |  |

| /CPU_RD      | Input        | HOST I/O Read                             |  |

| MASTER_CK    | Input        | 25.2 MHz Clock (50.4MHz/2)                |  |

| /CPU_WR      | Input        | HOST I/O Write                            |  |

| /ETRG        | Input        | Exciting Trigger                          |  |

| PRB_ID[0-4]  | Input        | Probe Identity Number                     |  |

|              |              | PROBE_ID[3] : default Low                 |  |

|              |              | PRB_ID[3] is not used.                    |  |

| TDI          | Input        | CPLD download TDI                         |  |

| TMS          | Input        | CPLD download TMS                         |  |

| TCK          | Input        | CPLD download TCK                         |  |

| TDO          | Output       | CPLD download TDO                         |  |

| HV_ON        | Output       | High: High Voltage On                     |  |

|              |              | Low: High Voltage Off                     |  |

|              |              | High Voltage On when probe connect to the |  |

|              |              | system                                    |  |

| /AD_EN       | Output       | A/D Converter Enable                      |  |

|              |              | Default Low                               |  |

| INIT_MODE[2] | Output       | BFIC Initial Mode                         |  |

|              |              | Real Mode: High                           |  |

|              |              | Download Mode : Low                       |  |

| /TX_MASK     | Output       | Tx Fire Disable                           |  |

|              |              | Display Low under Probe Disconnection or  |  |

|              |              | Freeze mode                               |  |

| /P_WR          | Output | BFIC P Register Write Strobe Use it when latch the Scanline on BFIC            |

|----------------|--------|--------------------------------------------------------------------------------|

| /BFIC_CS[0-1]  | Output | BFIC Chip Select  /BFIC_CS[0] : A/D Channel 0-3  /BFIC_CS[1] : A/D Channel 4-7 |

| /BFIC_RST      | Output | BFIC Reset                                                                     |

| /DATA_RD       | Output | Host Data Read                                                                 |

| /DATA_WR       | Output | Host Data Write                                                                |

| /DATA_EN       | Output | Host Data Enable                                                               |

| BFIC_ADDR[0-2] | Output | BFIC Address                                                                   |

# 2.3.2 Connector signals between DSC and FE

| Name              | 1/0    | Description                                      |

|-------------------|--------|--------------------------------------------------|

| ADDR[0-5]         | Input  | HOST Address                                     |

| FE_CTRL_CLK       | Input  | Front End Control Clock                          |

|                   |        | MT8816 Control Clock 16 ea                       |

|                   |        | HVSW Clock 24 ea                                 |

| /FE_CTRL_LE       | Input  | HVSW Latch Enable                                |

| FE_CTRL_RST       | Input  | MT8816 Reset                                     |

| FE_CTRL_ADDR[0-5] | Input  | MT8816 Address 0-15                              |

| FE_CTRL_DATA[0-7] | Input  | MT8816 Control                                   |

|                   |        | AY[0-2]=DATA[0-2]                                |

|                   |        | CPSW_DATA,CS = DATA[3]                           |

|                   |        | HVSW Control                                     |

|                   |        | /HVSW_DATA[0-3]=DATA[4-7]                        |

| SCANLINE[0-7]     | Input  | Scanline 0-255                                   |

| SYNTHETIC         | Input  | Low: Normal Tx                                   |

|                   |        | High: Synthetic Tx                               |

| CTRL_RESERVED     | Input  | Reserved / Default Low                           |

| FREEZE            | Input  | High: Freeze                                     |

|                   |        | Low : Real                                       |

| 25.2MHZ           | Input  | Master Clock 25.2MHZ                             |

| /EX_TRG           | Input  | Exciting Trigger                                 |

| /B_EOF            | Output | Beamforming Data Enable                          |

|                   |        | Use it on MPIC MGA015 of DSC                     |

| /OF               | Input  | One Frame                                        |

| /RP               | Input  | Rate Pulse                                       |

| /RPT              | Input  | Rate Pulse Train                                 |

| TGC_D[0-7]        | Input  | TGC Data                                         |

| T_SBCLK           | Output | Battery Clock                                    |

| T_SBDATA          | Output | Battery Data                                     |

| PRINT_REMOTE      | Input  | Echo Printer Remote                              |

| B_FREEZE_REMOTE   | Output | Freeze/Remote                                    |

|                   |        | The switch on the VET probe is using for toggle. |

|                   |        | Using for Freeze, press it short.                |

|                   |        | Using for Store, press it long (over 3secs.)     |

| FP[0-2]           | Input  | Focal Point / FP[2] = Default Low                |

| CLK_120KHZ        | Input  | Power Clock 120KHZ                               |

| CLK_240KHZ  | Input  | Power Clock 240KHZ  |

|-------------|--------|---------------------|

| VP5D        | Output | +5V                 |

| VP3.3D      | Output | +3.3V               |

| VP12A       | Output | +12V                |

| VP5A        | Output | +5V                 |

| VN5A        | Output | -5V                 |

| /CPU_WR     | Input  | Host Write          |

| /CPU_RD     | Input  | Host Read           |

| EXT_B[0-16] | Output | Beamforming Data    |

| LCDVR_A     | Output | LCD Brightness Knob |

| LCDVR_B     | Output | LCD Brightness Knob |

| GAIN_A      | Output | GAIN Knob           |

| GAIN_B      | Output | GAIN Knob           |

| NEAR_A      | Output | NEAR Knob           |

| NEAR_B      | Output | NEAR Knob           |

| FAR_A       | Output | FAR Knob            |

| FAR_B       | Output | FAR Knob            |

# 2.3.3 Connector signals between Power and FE

| Name         | 1/0              | Description                                 |  |  |  |

|--------------|------------------|---------------------------------------------|--|--|--|

| PRINT_REMOTE | Output           | Echo Printer Remote                         |  |  |  |

| CLK_120KHZ   | Output           | Power Clock 120KHZ                          |  |  |  |

| CLK_240KHZ   | Output           | Power Clock 240KHZ                          |  |  |  |

| HV_ON        | Output           | High: High Voltage On Low: High Voltage Off |  |  |  |

| T_SBCLK      | Input            | Battery Clock                               |  |  |  |

| T_SBDATA     | Input/Outp<br>ut | Battery Data                                |  |  |  |

| VP5D         | Input            | +5V                                         |  |  |  |

| VP3.3D       | Input            | +3.3V                                       |  |  |  |

| VP12A        | Input            | +12V                                        |  |  |  |

| VP5A         | Input            | +5V                                         |  |  |  |

| VN5A         | Input            | -5V                                         |  |  |  |

| HVP          | Input            | +80V                                        |  |  |  |

| HVN          | Input            | -80V                                        |  |  |  |

# 2.3.4 Connector signals between FE Adapter and FE

| Name            | 1/0        | Description                       |  |  |  |

|-----------------|------------|-----------------------------------|--|--|--|

| PLS_OUT[0-15]   | Input/Outp | Ultrasound Echo                   |  |  |  |

|                 | ut         |                                   |  |  |  |

| +80VA           | Output     | +80V                              |  |  |  |

| -80VA           | Output     | -80V                              |  |  |  |

| +5VA            | Output     | +5V                               |  |  |  |

| /HVSW_DATA[0-3] | Output     | High Voltage Control Data         |  |  |  |

| HVSW_CLK        | Output     | High Voltage Control Clock        |  |  |  |

|                 |            | 3.15MHz Clock 24 ea               |  |  |  |

| /HVSW_LE        | Output     | High Voltage Control Latch Enable |  |  |  |

| PRB_ID[0-4]     | Input      | Probe ID                          |  |  |  |

| /PRB_INS        | Input      | Low : Probe Inserted              |  |  |  |

|                 |            | High: Probe Not Inserted          |  |  |  |

| FREEZE_REMOTE   | Input      | Freeze Remote                     |  |  |  |

|                 |            | Short Click: Freeze               |  |  |  |

|                 |            | Long Click : Store                |  |  |  |

# 2.3.5 Connector signals between FE Adapter and SPC(System Probe Connector)

| Name            | 1/0        | Description                       |  |  |  |

|-----------------|------------|-----------------------------------|--|--|--|

| PLS_OUT[0-15]   | Input/Outp | Ultrasound Echo                   |  |  |  |

|                 | ut         |                                   |  |  |  |

| +80VA           | Output     | +80V                              |  |  |  |

| -80VA           | Output     | -80V                              |  |  |  |

| +5VA            | Output     | +5V                               |  |  |  |

| /HVSW_DATA[0-3] | Output     | High Voltage Control Data         |  |  |  |

| HVSW_CLK        | Output     | High Voltage Control Clock        |  |  |  |

|                 |            | 3.15MHz Clock 24 ea               |  |  |  |

| /HVSW_LE        | Output     | High Voltage Control Latch Enable |  |  |  |

| PRB_ID[0-4]     | Input      | Probe ID                          |  |  |  |

| /PRB_INS        | Input      | Low : Probe Inserted              |  |  |  |

|                 |            | High: Probe Not Inserted          |  |  |  |

| FREEZE_REMOTE   | Input      | Freeze Remote                     |  |  |  |

|                 |            | Short Click: Freeze               |  |  |  |

|                 |            | Long Click: Store                 |  |  |  |

# 2.3.6 Connector signals between SPC(System Probe Connector) and Probe

|   | 1        | 2        | 3        | 4        | 5        | 6        |

|---|----------|----------|----------|----------|----------|----------|

| Α | ECHO 0   | GND      | ECHO 1   | GND      | ECHO 2   | GND      |

| В | GND      | ECHO 3   | GND      | ECHO 4   | GND      | ECHO 5   |

| С | ECHO 6   | GND      | ECHO 7   | GND      | ECHO 8   | GND      |

| D | GND      | ECHO 9   | GND      | ECHO 10  | GND      | ECHO 11  |

| E | ECHO 12  | GND      | ECHO 13  | GND      | ECHO 14  | ECHO 15  |

| F | N.C.     | N.C.     | GND      | + 80 V   | + 80 V   | GND      |

| G | GND      | - 80 V   | - 80 V   | GND      | + 5 V    | GND      |

| Н | /DATO 0  | /DATA 1  | GND      | /DATA 2  | /DATA 3  | GND      |

| J | Remote   | HVSW_CLK | /HVSW_LE | N.C.     | N.C.     | PRB_ID 0 |

| K | PRB_ID 1 | PRB_ID 2 | GND      | PRB_ID 3 | PRB_ID 4 | /PRB_INS |

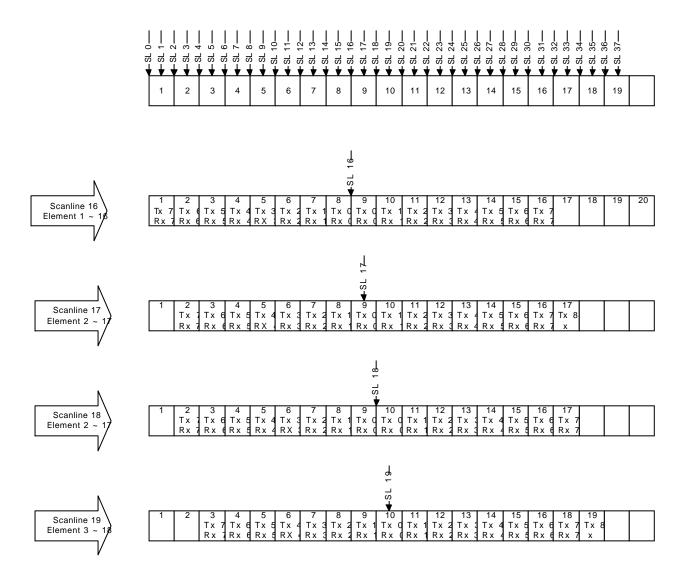

#### 2.4 Scanline Definition

#### 2.4.1 Normal Mode

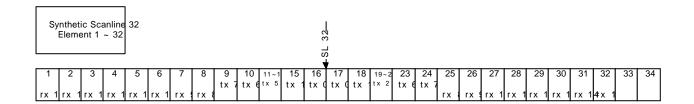

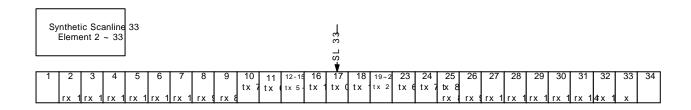

## 2.4.2 Synthetic Mode

| Synthetic Mode : |            |           |      |          |      |

|------------------|------------|-----------|------|----------|------|

| Scanline         | Element 16 | Firing    |      | usec     | HVSW |

| Control          | Firing     | Ele       | men  | t 16     | Echo |

| Signal           | . Echo Pro | cessor IC | Nori | nal Mode |      |

| Synthetic Mode   |            |           |      |          |      |

#### 2.5 Pulser vs Elements

#### 2.6 Detail Description

#### 2.6.1 TGC Amp

The main chip of TGC Amp is AD604. Two Variable Gain Amp is located inside of the chip and they are composed of 2 channels TGC Amp. The ultrasound signal that was reflected or propagated from a medium can compensate by Variable Gain as time, that is to say it is a proceeded distance, at this stage.

Gain Range :  $0 \sim 48 \text{ dB (Preamp Gain} = + 14 \text{ dB)}$

Input resistance : 300 kohm

Variable Gain Scaling : 20 dB/V

Gain [dB] =  $20[dB/V] * TGC\_Curve[v] - 5 [dB]$

Output Impedance : 2 ohm

Load resistance > 500 ohm

Reference Voltage : 2.5V (Gain Scaling 20 dB/V)

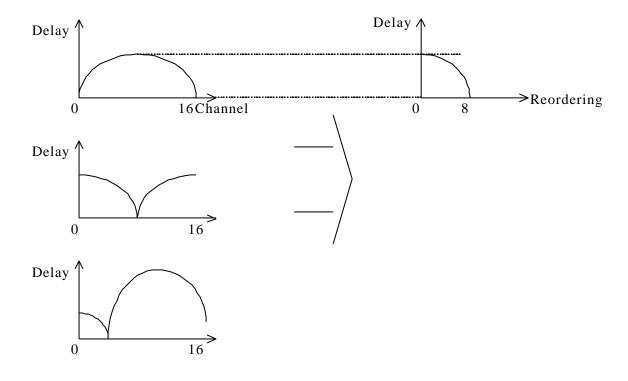

#### 2.6.2 Reordering

One MT8816 generate 16 x8 MUX.

It is controlled by Scan Lind regardless TX Focal Point or Probe type.

#### [Normal Tx Mode]

The ultrasound signal symmetrically controls the reordering around Center Element. But at the point of BFIC Channel, the Center of signal could be moved as Scanline because it has sixteen MUX (6x1) as High Voltage Switching IC in the Probe Box.

Thus it is possible to control BFIC RX Control date size by reordering this signal.

1

#### [Synthetic Tx mode]

To achieve 1 scanline image, the element that used Tx or Rx is the same in Normal Tx mode.

Under Synthetic Tx mode, it is the same as Tx element but RX receive the first signal from the center 16 elements and receive again the second signal from the near side 16 elements. As the result, RX generate 32 channel image in MGA015A Mid Processor ASIC by adding two scanline Beamforming data in RF domain

2.6.3 LPF

Low-Pass Filter located the edge of the Analog Receiver Channel is worked both noise suppression as stop band and Anti-aliasing Filter as reduce aliasing caused by high frequency probe such as 7.5MHz Probe

[Figure 5. Low-Pass Filter]

A/D clock is 25.2 MHz and maximum center frequency of probe is 7.5MHz.

And 3dB cut off frequency for Trade-off is 10MHz.

LPF works as Bessel filter and constructs the circuit by 4<sup>th</sup> step for reducing a ringing.

#### 2.6.4 Beamforming IC MCB014A

For Reordering, it is necessary 8 Channel A/D Converters. BFIC has 4 Channels. To make a Beamforming, two BFICs are required.

Tow's Compliment is output and Bit 1 to 16 is used at the last output.

Both of main clock and the last output data rate are 25.2Mhz. It is possible to control Tx Delay by twice frequency and to control Tx Period under 25.2MHz, 40nsec.

To prepare the next calculation of scanline during Beamforming, have to provide the next scanline between /RPT rising point and /ETRG rising point.

## 2.7 PCB BOARD LAY OUT

#### **2.7.1 F/E TOP SIDE**

## 2.7.2 F/E BOTTOM SIDE

## 2.8 Timing Chart

## 2.8.1 Normal TX Focusing

If Next scanline is M Mode Line, then N+1 means M mode scanline.

## 2.8.2 Synthetic Tx Focusing

## 2.8.3 Control Timing

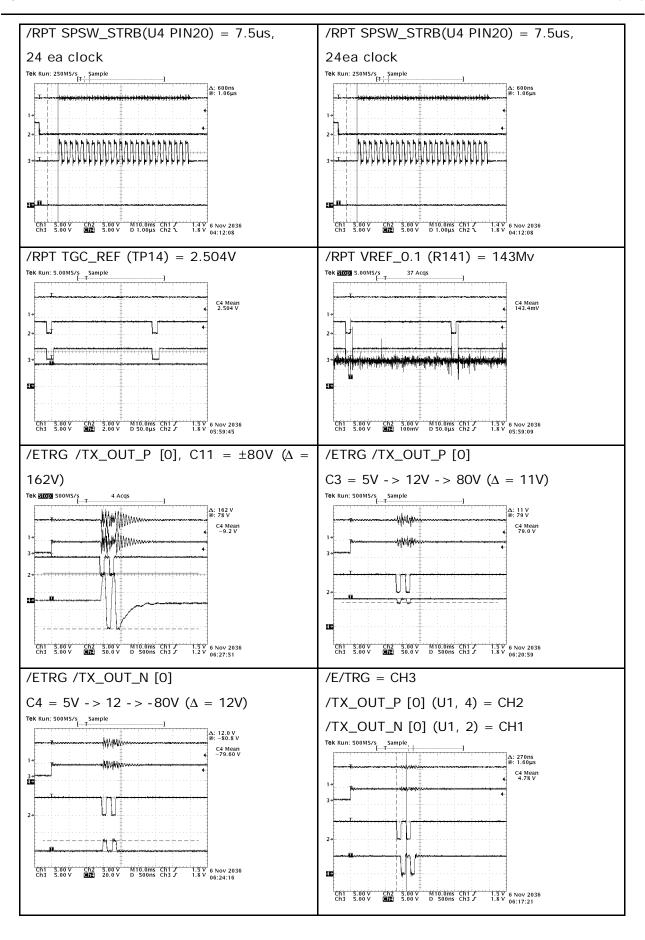

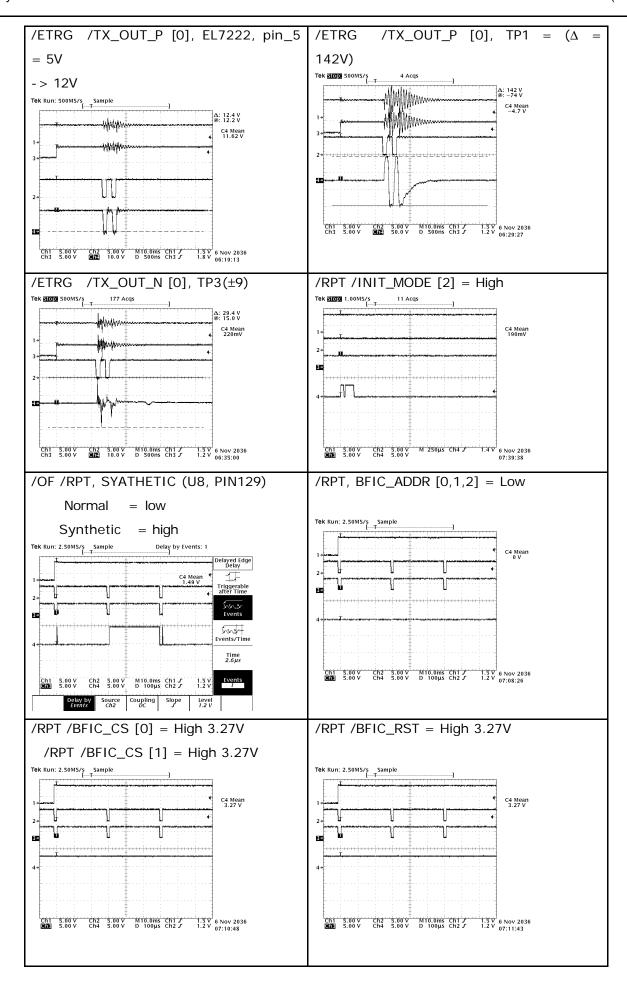

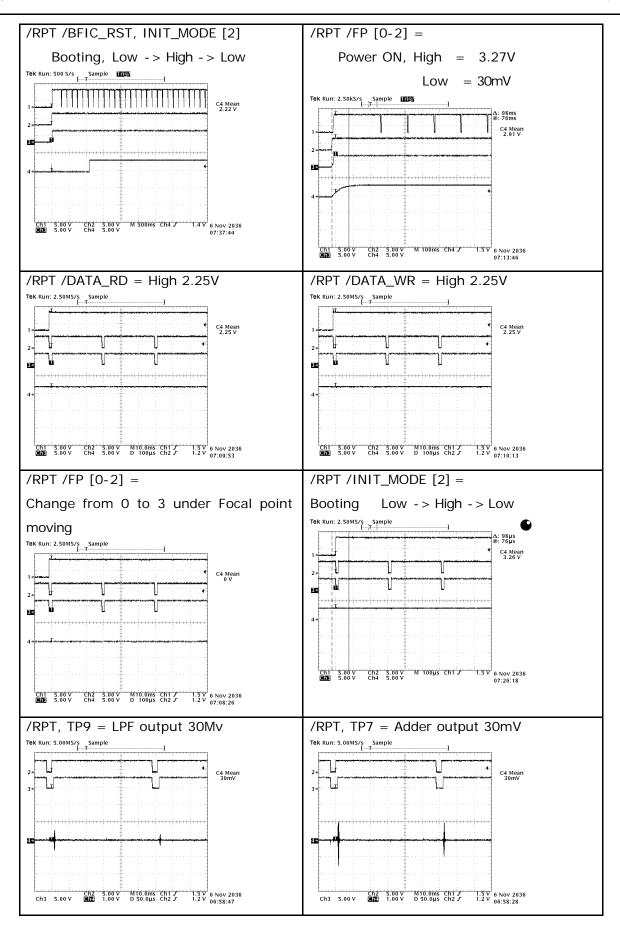

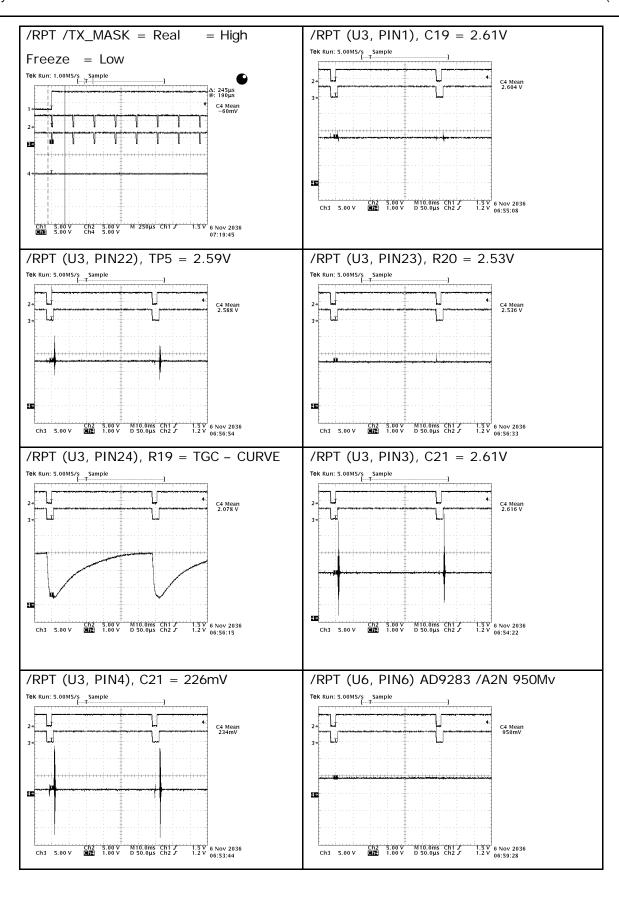

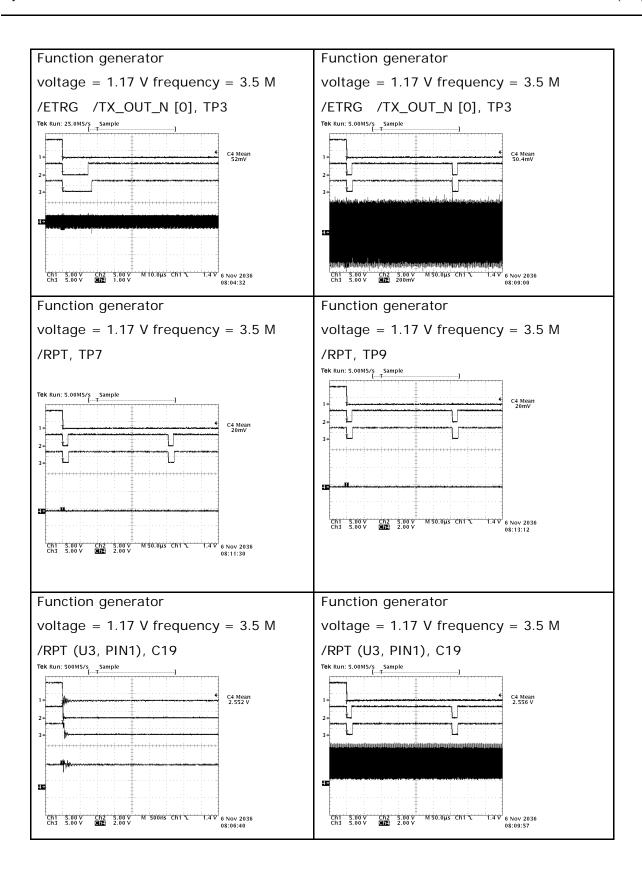

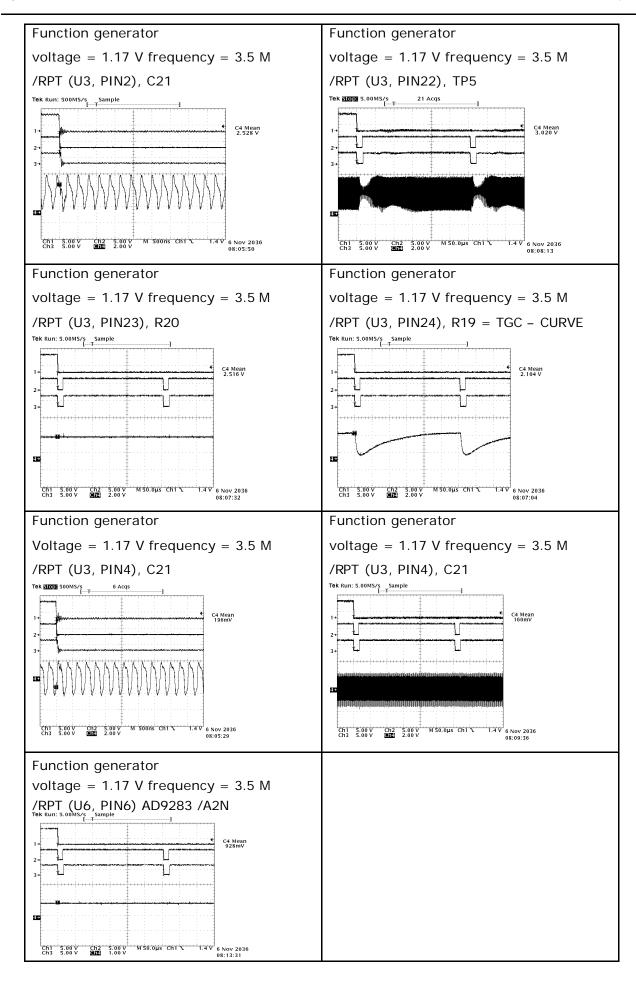

#### 2.9 Wave Form

#### 3.DSC Board

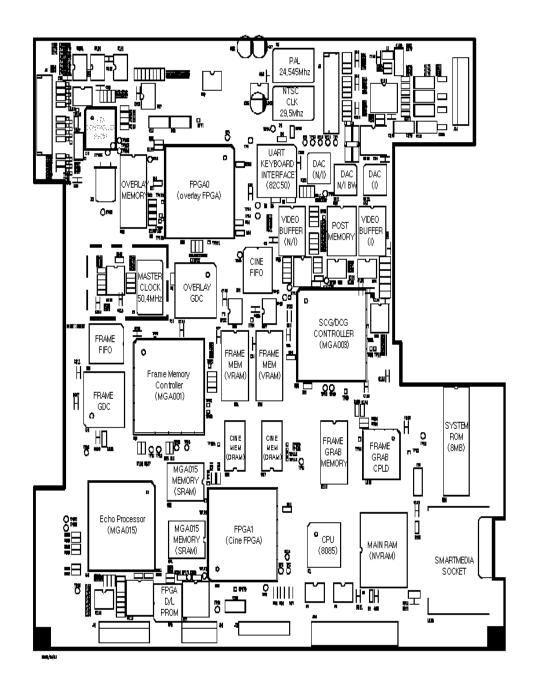

#### 3.1. Description Overall

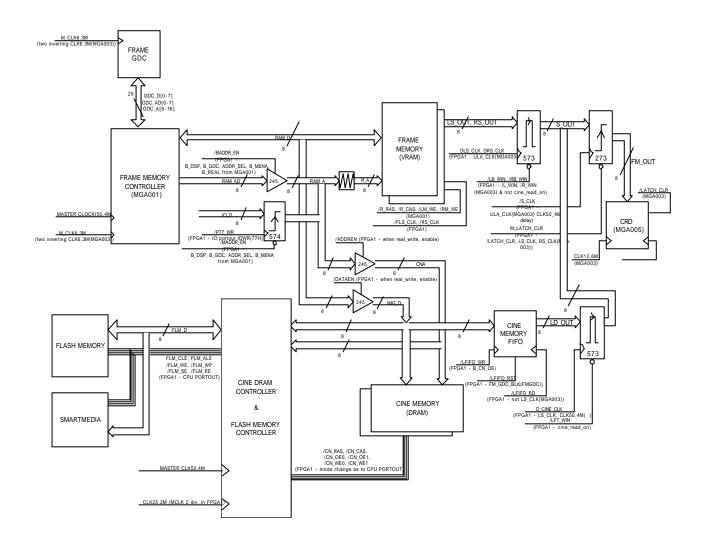

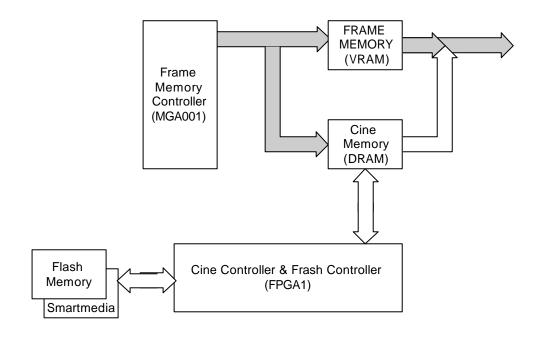

- B/F data pass to FIFO through MID Processor and the data is sampling by ADCLK on Clock Generator (MGA003) and then transfer to Frame Average (MGA001).

- MGA003 generates the Clock by integrating the standard signal (/OF, /RP, /EADC) come form RTC Controller (FPGA0), Sampling Clock information as Scan Line inside SCG•DCG ROM and Display Clock information.

- MGA001 works as Frame Average Function by using /OF, /RP, /EADC come from RTC Controller (FPGA0) under controlling Frame GDC, and then transfer the data to Frame Memory and Cine Memory.

- In Real mode, the data come from MGA001A is stored both Frame Memory and Cine Memory simultaneously. But the data come from Frame Memory transfer to CRD (MGA005).

- In Cine mode, the data come from MGA001A is not transfer either Frame Memory or Cine Memory and the data stored in Cine Memory pass to CRD (MGA005) and display on the screen.

- The Port out Command in CPU of Cine Controller (FPGA1) control the Cine Memory.

- The data come from Frame Memory (or Cine memory) is variable DCG rate each H-Sync. CRD (MGA005) interpolate it by 12.6MHz unit in 1D (Horizontal Interpolation) and make a data as equal then pass it to Post Memory for displaying.

- Port out command of CPU input into Overlay GDC. Overlay GDC generates Overlay data and then pass them to Post memory. And generate the general Control signals that are necessary in Overlay.

- Post Memory integrates the data come from CRD and Overlay GDC and makes the image adapted on 640x480. Then pass it to Video Buffer (AL422) and display it on the LCD (or Monitor).

- Video Buffer (AL422) receive the control signals come from Video Output Controller to adjust Refresh Rate of LCD (or Monitor) and output the Image data as 25.2MHz and then transfer them to DAC (TDA8775).

## 3.2. Block Diagram

# DSC Block Diagram of mysono

## 3.3 Signal Definition

| Name              | 1/0    | Description                  |  |

|-------------------|--------|------------------------------|--|

| A[0-15]           | Input  | HOST Address                 |  |

| AD[0-15]          |        | HOST DATA                    |  |

| RST               |        | 8085 CPU RESET               |  |

| ALE               | OUTPUT | DATA ADDRES ENABLE           |  |

| /IO_W             | OUTPUT | IO CHIP WRITE ENABLE         |  |

| /RD               |        | IO READ                      |  |

| IO_D[0-7]         |        | UPD72020 DATA BUS            |  |

| /OL_GDC_RAS       |        | OVERLAY GDC RAS              |  |

| OL_GDC_BLK        |        | OVERLAY GDC BLK              |  |

| /OL_GDC_DBIN      |        | OVERLAY GDC DBIN             |  |

| /OL_GDC_RD        |        | OVERLAY GDC READ             |  |

| /OL_GDC_WR        |        | OVERLAY GDC WRITE            |  |

| CLK3.15           |        | POWER CLOCK 3.15Mz           |  |

| ADDR[0-5]         | Input  | HOST Address                 |  |

| FE_CTRL_CLK       | Input  | Front End Control Clock      |  |

|                   |        | MT8816 Control Clock 16      |  |

|                   |        | HVSW Clock 24 ea             |  |

| /FE_CTRL_LE       | Input  | HVSW Latch Enable            |  |

| FE_CTRL_RST       | Input  | MT8816 Reset                 |  |

| FE_CTRL_ADDR[0-5] | Input  | MT8816 Address 0-15          |  |

| FE_CTRL_DATA[0-7] | Input  | MT8816 Control               |  |

|                   |        | AY[0-2]=DATA[0-2]            |  |

|                   |        | CPSW_DATA,CS = DATA[3]       |  |

|                   |        | HVSW Control                 |  |

|                   |        | /HVSW_DATA[0-3]=DATA[4-7]    |  |

| SCANLINE[0-7]     | Input  | Scanline 0-255               |  |

| SYNTHETIC         | Input  | Low: Normal Tx               |  |

|                   |        | High: Synthetic Tx           |  |

| CTRL_RESERVED     | Input  | Reserved                     |  |

|                   |        | Default Low                  |  |

| FREEZE            | Input  | High: Freeze                 |  |

|                   |        | Low: Real                    |  |

| 25.2MHZ           | Input  | Master Clock 25.2MHZ         |  |

| /EX_TRG           | Input  | Exciting Trigger             |  |

| /B_EOF            | Output | Beamforming Data Enable      |  |

|                   |        | Use it on MPIC MGA015 of DSC |  |

| /OF             | Input  | One Frame                            |  |

|-----------------|--------|--------------------------------------|--|

| /RP             | Input  | Rate Pulse                           |  |

| /RPT            | Input  | Rate Pulse Train                     |  |

| TGC_D[0-7]      | Input  | TGC Data                             |  |

| T_SBCLK         | Output | Battery Clock                        |  |

| T_SBDATA        | Output | Battery Data                         |  |

| /CPU_RD         | Input  | Host Read                            |  |

| EXT_B[0-16]     | Output | Beamforming Data                     |  |

| LCDVR_A         | Output | LCD Brightness Knob                  |  |

| LCDVR_B         | Output | LCD Brightness Knob                  |  |

| GAIN_A7         | Output | GAIN Knob                            |  |

| GAIN_B          | Output | GAIN Knob                            |  |

| NEAR_A          | Output | NEAR Knob                            |  |

| NEAR_B          | Output | NEAR Knob                            |  |

| FAR_A           | Output | FAR Knob                             |  |

| PRINT_REMOTE    | Input  | Echo Printer Remote                  |  |

| B_FREEZE_REMOTE | Output | Freeze/Remote                        |  |

|                 |        | The switch on the probe is using for |  |

|                 |        | toggle.                              |  |

|                 |        | Using for Freeze, press it short.    |  |

|                 |        | Using for Store, press it long (over |  |

|                 |        | 3secs.)                              |  |

| FP[0-2]         | Input  | Focal Point                          |  |

|                 |        | FP[2] = Default Low                  |  |

• NOTE: Refer to Article 5. in chapter 2. [ASIC PIN definition]

#### 3.4 Detail Description

#### 3.4.1 B/W Data Receiving & FM Storing Part

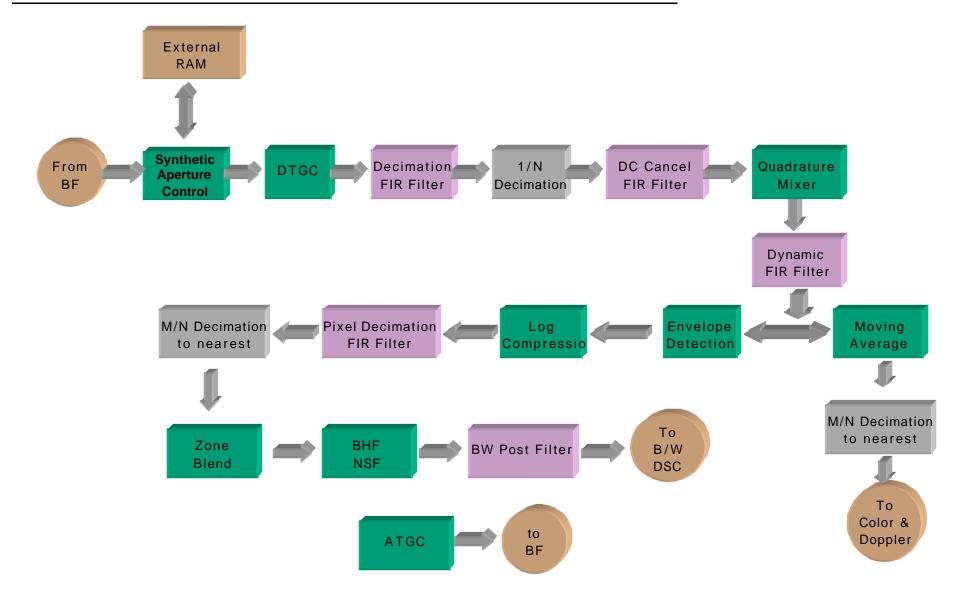

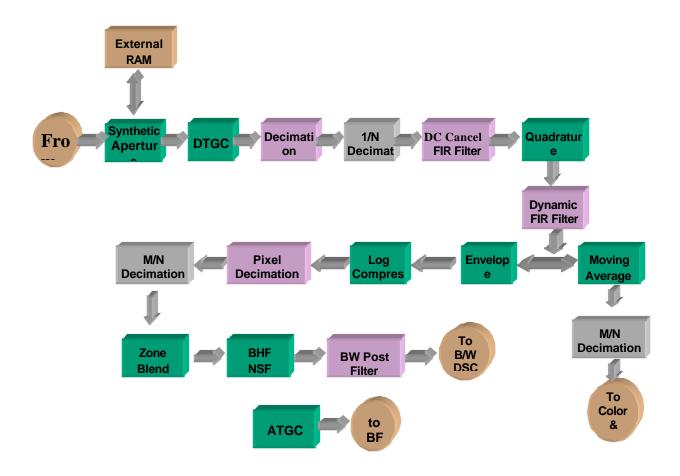

#### 3.4.1.1 Mid-Processor (MGA015A)

- Mid-processor plays as converter RF data come from F/E board into BW data that can

use in DSC pass through several digital signal processing.

- MGA015A ASIC clock divides system master clock 50.4MHz into 25.2MHz on MGA003 and pass through it to Clock buffer. As the result, it uses 25.2MHz.

- The data of Internal MGA015A is controlled by CPU Portout downloading. Host controller (FPGA1-host data, host address, host\_wr, host\_rd) works as the download interface.

- RF data, the first TX/RX result come from B/F, is stored SRAM in MGA015A. But external SRAM is necessary to display BW data that generated by summing up the second R/F data of TX/RX result.

- MGA015A makes /BW\_CLK\_0 that 74HCT574 located on the back stage is to latch the BW data. But because /BW\_CLK\_0 do not make any clock during /RP blank period, /RP the last data remain in 74HCT574. Thus the first sampling data in /RP enable period is possible to be the last data during hole /RP period. As the result, white spot symptom appears at near part on the image. To remove this symptom, use /MOD\_BW\_CLK\_0 include dummy clock. It clears 74HCT574 data within RP blank period.

Figure 1. Mid-Processor (MGA015)

#### 3.4.1.2 Pattern generator

- FPGA0 drives Pattern generator.

- Pattern generator is a block that makes a test pattern to check DSC function whether it works well or not.

- According to test pattern on/off, change from /BW\_OUT\_EN to /BW\_TST\_EN.

- Test pattern on/off is set by CPU portout.

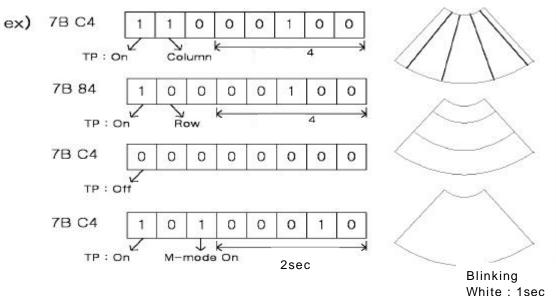

[Test pattern type and the bit value of 7BH port]

Bit7: test pattern on/off Bit6: Row/Colume selection

Bit5 : m-mode test pattern on/off Bit4~Bit0: increment value

White: 1sec Black: 2sec

#### 3.4.1.3 Before FM controller (MGA001)

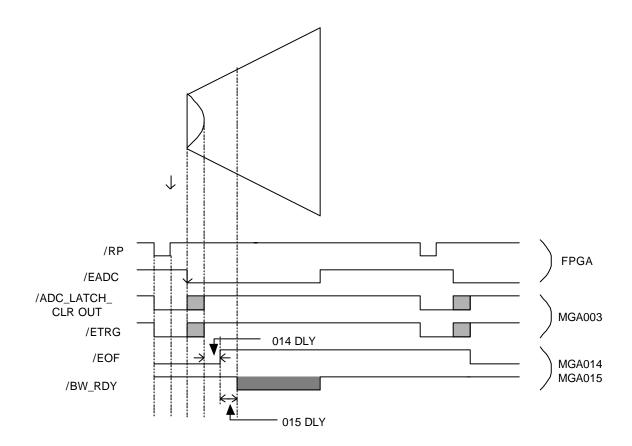

- BW data sampling get according to /AD\_LATCH\_CLK.

- /AD\_LATCH\_CLK is a clock that generated by masking ADCLK come form MGA003 into /EADC.

- Master reset of 74HCT27 is achieved by /AD\_LATCH\_CLR\_OUT. /AD\_LATCH\_CLR\_IN signal generated by MGA003 match the BW data sampling point as masking /BW\_RDY.

- Frame memory FIFO stores the BW data with scanline direction temporary and support to write the data on the Frame memory. To match the timing point, FIFO write clock uses an inverter type of /AD\_LATCH\_CLK.

- The clock that read Frame Memory FIFO receive the BW data using /EMPTY\_FLAG.

/ACK is a clock to read Frame FIFO and receive BW data using REQ and /EMPTY\_FLAG.

- REQ represent whether MGA001 is ready to BW data process and /EMPTY\_FLAG check whether the FIFO is empty.

#### 3.4.1.4 FM controller (MGA001)

MGA001 for exclusive use of FMC design to generate several signals under ASIC Technology.

- The related signals of Frame memory are DATA & Address Bus, Control signal such as /RAS, /CAS, /OE, /WE, etc.

- Data Bus of Frame memory is connected with Frame Average Logic at chip inside and average factor is 6ea. Mysono201 used 4ea among them.

- MGA001 use two clocks. Master clock is 50.4MHz and 6.3MHz clock same as Frame GDC. In case of 6.3MHz clock, use 6.3MHz half clock of MGA003 with the result of passing through inverter twice since clock slew rate is not fine.

- Frame GDC generate the standard signals such as FM\_GDC\_HS, FM\_GDC\_BLK, /FM\_GDC\_RAS, /FM\_GDC\_DBIN and perform the factor data and functions. However, for /FM\_GDC\_RAS signal, use /FM\_GDC\_RAS\_LATCH signal with latching the rising edge as 50.4MHz to match the necessary point at MGA001

- FMC is connected with address bus and data bus for Frame memory.

In M-mode, to store a designated scanline data in a designated FM address, the latch that portout the address form CPU is connected with address bus.

- M mode CPU portout latch output and 245buffer output of FMC address bus are working as either enabling or switching by BADDR\_EN and /MADDR\_EN that use integrating the signals come from MGA001 such as /DSP, /GDC, /ADDR\_SEL, /M\_ENA, /REAL according to mode status.

Service Manual

## 3.4.2 FRAME MEMORY & CINE MEMORY FLASH MEMORY PART

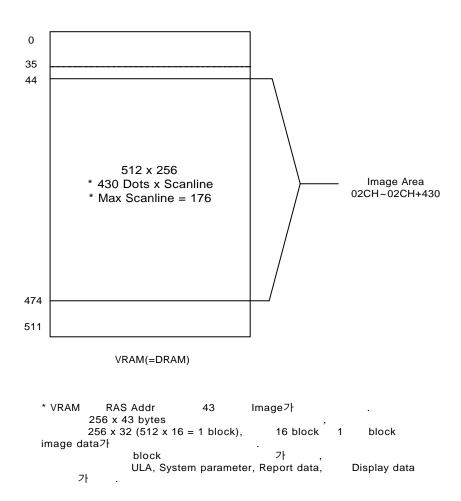

#### 3.4.2.1 Frame Memory (VRAM)

There is two Frame Memory type, RM and LM.

|                    | B – MODE | B/M – MODE | B/B - MODE | M-Mode   |

|--------------------|----------|------------|------------|----------|

| LEFT Frame Memory  | В        | В          | LB         | Not used |

| RIGHT Frame Memory | Not used | M          | RB         | М        |

- Operation for writing on Frame memory is achieved by MGA001 control signal such as /R\_RAS, /R\_CAS, /LM\_WE, /RM\_WE, etc.

- Operation for reading on Frame memory is recognized by Display clock at SAM. (cf.

VRAM = DRAM + FIFO) And latch it by 573 latch data.

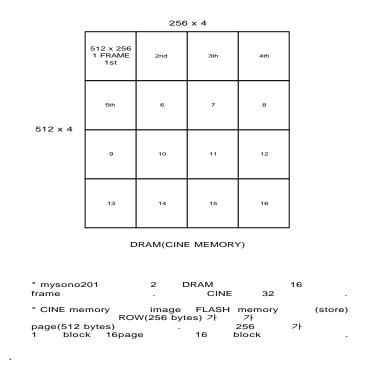

#### 3.4.2.2 Cine Memory (DRAM)

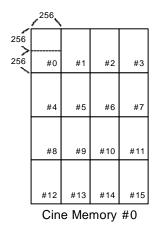

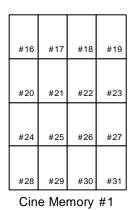

- Cine memory store total 32 frame and use for image store include Cine image.

- Cine memory controller (FPGA1) controls the cine memory.

- Under Real mode, Cine memory is stored with Frame memory at the same time using the data come from FMC directly and control signal such as /R\_RAS, /R\_CAS, /RM\_WE, /LM\_WE. But under Cine mode, data is output from Cine memory instead of FM and connected with Cine memory FIFO of DRAN back stage to work as VRAM.

- Frame memory data path and Cine memory data path meet at Data bus, called S\_OUT.

And 573 latch is enable by toggle signal of /LFT\_WIN, /LB\_WIN (or /RB\_WIN) according to mode.

#### DRAM Memory(CINE Memory) Map

Figure 1. Cine Memory Map

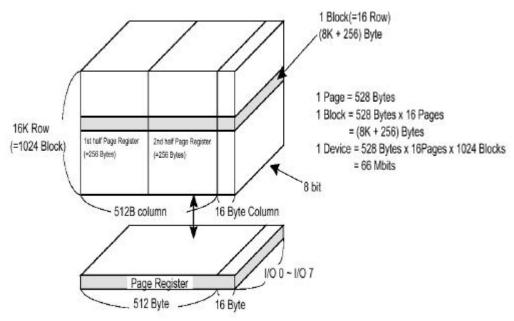

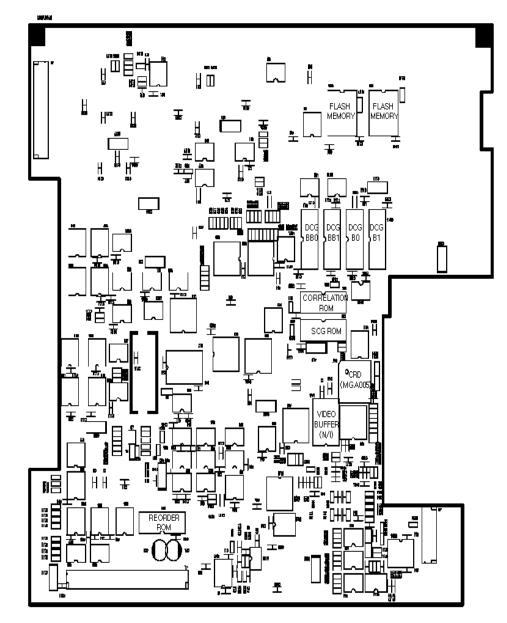

#### 3.4.2.3 Flash Memory

Flash memory is a NAND type and use a backup memory for image saving.

- It is controlled at Flash memory controller (FPGA 1) generated by CPU Portout.

- Flash memory control is achieved at Flash memory controller (FPGA1) under CPU portout. But as CPU controls by the control signals such as FLM\_CLE, FLM\_ALE, /FLM\_WE, /FLM\_RE that are selected through CPU portout, Flash memory controller work as simple interface.

Service Manual Published by SERTECH

## 1 Frame in Flash

Figure 2. Fresh Memory Map

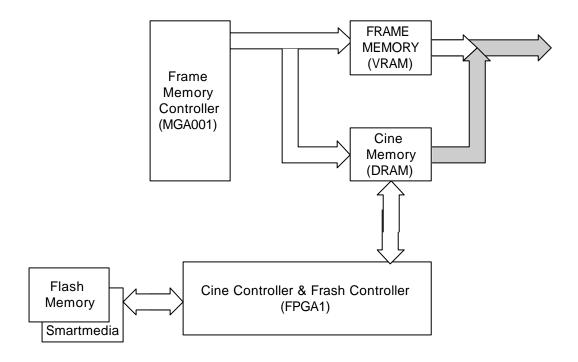

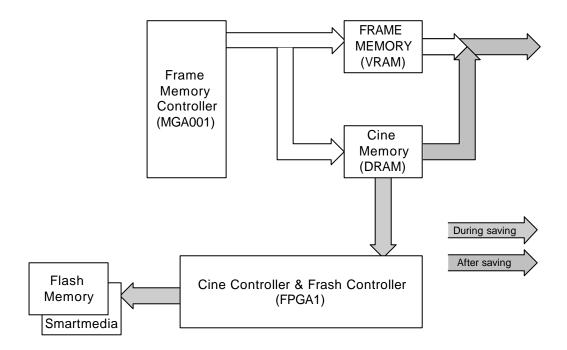

## 3.4.2.4 Memory Path by Mode

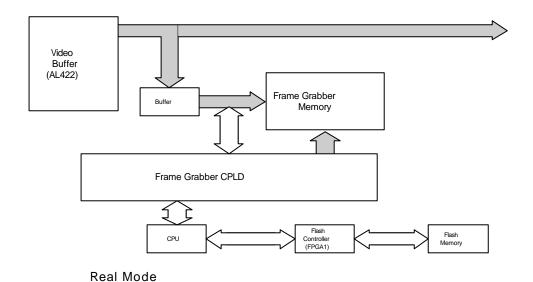

#### Real Mode

## Cine Mode

Flash Memory Save

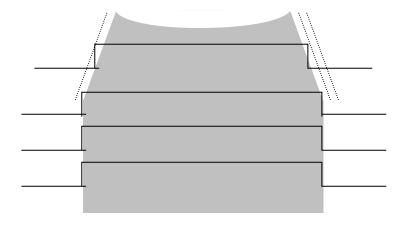

## 3.4.2.5 Scanline Masking Window

- When change the Mode (BM→B or BB→B) or control the Gain, an unsuitable image display on the monitor due to save unsuitable data out of image area since VRAM address control unstable

- Display clock is a regular according to probe element.

It occurs as much as scanline.

Display clock is constant by probe element. That is to say, Display clock generates as much as scanline. Thus, if count a number of scanline and use it for the Master reset of 74HCT27 on the front stage of MGA005, the dummy scanline problem can be solved by pass through only the data under image area. The other data out of image area is reset.

However, due to only the display clock is available that pass through the disable period of /LATCH\_CLR, make a new signal of /M\_LATCH\_CLR and use to /MR in 74HCT273.

#### 3.4.3 CRD, Graybar, Overlay Post Memory Part

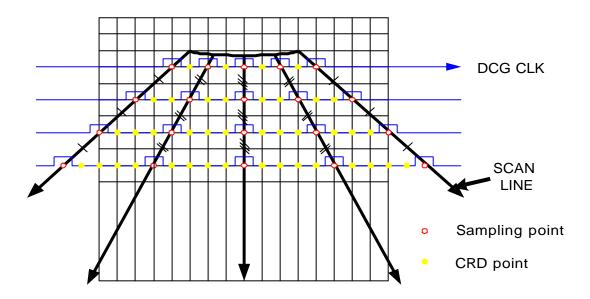

#### 3.4.3.1 CRD

- Display the ultrasound image of the Convex probe on the monitor, system recognize and read the data of Frame memory by Display clock that generated on DCG (Display Clock Generator).

- One scanline will be interpolated to the Horizontal Sync (HSYNC) as fixed Scanline number from the system and the frequency of interpolation DCG Clock will be changed whenever the HSYNC is generated according to the Vertical Sync (VSYNC).

The image from Far-Field is interpolated as low frequency DCG Clock and there is a possibility of mosaic problem on actual display.

- The CDR Logic uniformly converts the frequency of signal as 12.6 MHz that input to the Monitor by 1D interpolation to horizontal axis for the data that is interpolated from the Frame Memory as Monitor Dot Clock 12.6 MHz.

- MGA003 gives a parameter required for CRD, treat it as Dot Clock.

Input clock receive the data using DULA\_CLK\_50.

- The parameter that need to CRD get from MGA003, and process it by Dot clock.

But the received clock gets the data by using DULA\_CLK\_50 that delays the ULA clock.

#### 3.4.3.2 Graybar

- Graybar generate 4 Bit data come from MGA003.

- The signal related with Graybar is as follows;

- GRAY\_OE: Controlled by MGA003 and manages the output point of Graybar data

- CRD\_O[4-7]: Graybar data and share both MGA005 output bus and upper 4bit.

- /BMODE\_EN : It is a Enable signal to control data output of MGA005

The basic schema of Graybar is as follows;

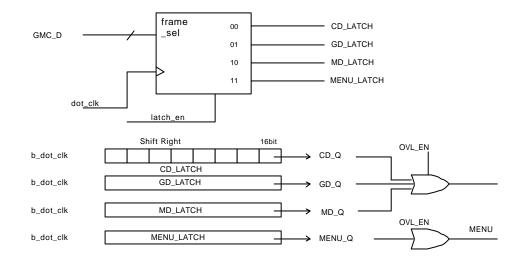

## 3.4.3.3 Overlay

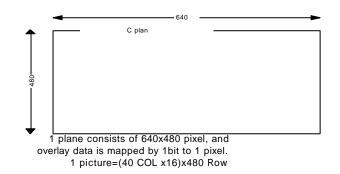

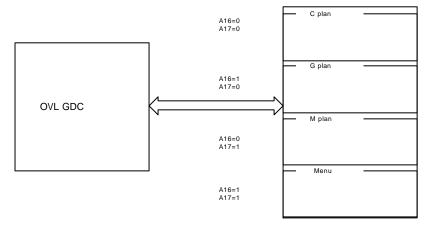

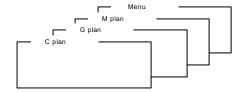

- Overlay data is generated by using overlay memory with controlling overlay GDC by CPU. It goes to FPGAO and processed to C, G, M, MENU then the final output is overlay data and menu data. The data processing method is described as below block diagram. GMC-D is the data that is processed by overlay GDC in overlay memory and 12.6 MHz of dot\_clock is used.

- This data is serially output from FPGAO and combined with image in post memory.

Mysono201 Medison Co.,Ltd.

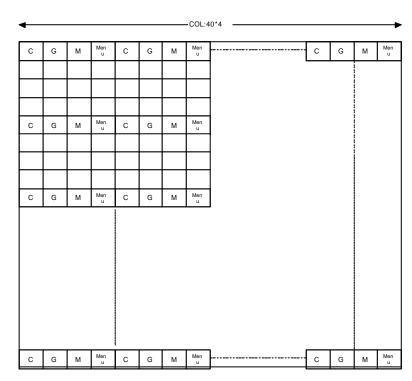

## 3.4.3.4 Overlay Control Schema

GDC manage the external RAM address like above picture, and each picture plane is overlaped like following.

<DRAM Memory allocation>

When GDC write to DRAM: Column:

DRAM\_A0 <= OL\_AD16 DRAM\_A1 <= OL\_AD17

Row:

Row:0

Row:4

Row:8

Row:4\*480

DRAM\_A0 <= 0 DRAM\_A1 <= 0

When GDC write to DRAM:

Column:

DRAM\_A0,1: 0~3 in a GDC\_RAS pulse

Row:

DRAM\_A0 <= 0 DRAM\_A1 <= 0

#### 3.4.3.5 Post Memory

Post memory consists of SRAM. It combines an image data and an overlay data into the data displayed on the screen.

It could change the display settings such as Gamma setting by control the data in Post memory.

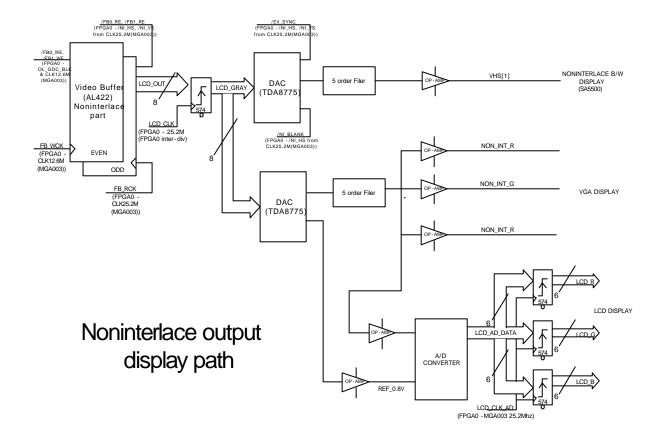

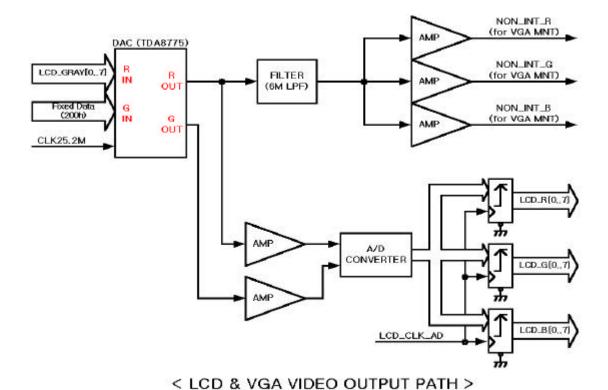

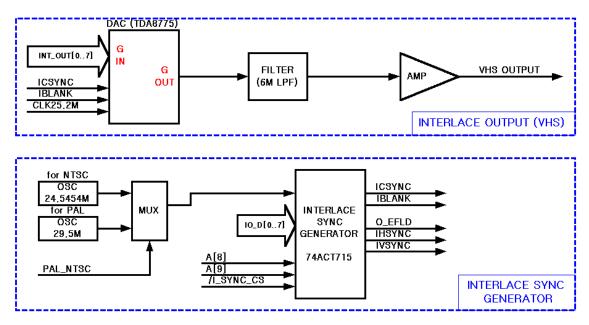

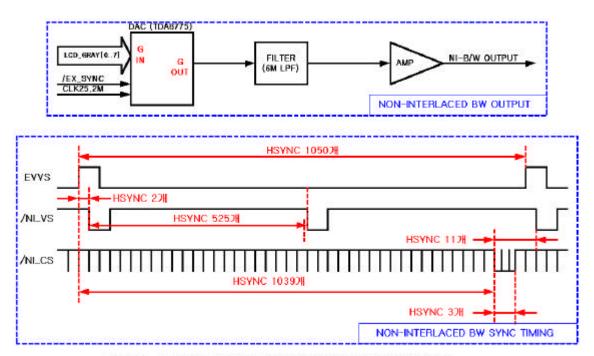

### 3.4.4 Noninterlace Output Display Path Port

#### 3.4.4.1 Function

- → Non-Interlaced B/W Monitor

(Recommended by Medison. Medison supplies this monitor.)

- → VGA Monitor (We does not fixed specify model. You can use any type.)

- → NTSC or PAL VHS Monitor (We does not fixed specify model. You can use any type.)

- → NTSC or PAL VCR Record (Only Record. Does not support VCR Play Function.)

- → B/W Echo Printer